- 您现在的位置:买卖IC网 > PDF目录177664 > LC5512MB-75F256I (LATTICE SEMICONDUCTOR CORP) PDF资料下载

参数资料

| 型号: | LC5512MB-75F256I |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 中文描述: | EE PLD, 9.5 ns, PBGA256 |

| 封装: | FPBGA-256 |

| 文件页数: | 1/95页 |

| 文件大小: | 923K |

| 代理商: | LC5512MB-75F256I |

当前第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页

www.latticesemi.com

1

5kmx_12.4

ispXPLD 5000MX Family

3.3V, 2.5V and 1.8V In-System Programmable

eXpanded Programmable Logic Device XPLD Family

February 2010

Data Sheet

TM

2010 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

Features

Flexible Multi-Function Block (MFB)

Architecture

SuperWIDE logic (up to 136 inputs)

Arithmetic capability

Single- or Dual-port SRAM

FIFO

Ternary CAM

sysCLOCK PLL Timing Control

Multiply and divide between 1 and 32

Clock shifting capability

External feedback capability

sysIO Interfaces

LVCMOS 1.8, 2.5, 3.3V

– Programmable impedance

– Hot-socketing

– Flexible bus-maintenance (Pull-up, pull-

down, bus-keeper, or none)

– Open drain operation

SSTL 2, 3 (I & II)

HSTL (I, III, IV)

PCI 3.3

GTL+

LVDS

LVPECL

LVTTL

Expanded In-System Programmability (ispXP)

Instant-on capability

Single chip convenience

In-System Programmable via IEEE 1532

Interface

Infinitely reconfigurable via IEEE 1532 or sys-

CONFIG microprocessor interface

Design security

High Speed Operation

4.0ns pin-to-pin delays, 300MHz fMAX

Deterministic timing

Low Power Consumption

Typical static power: 20 to 50mA (1.8V),

30 to 60mA (2.5/3.3V)

1.8V core for low dynamic power

Easy System Integration

3.3V (5000MV), 2.5V (5000MB) and 1.8V

(5000MC) power supply operation

5V tolerant I/O for LVCMOS 3.3 and LVTTL

interfaces

IEEE 1149.1 interface for boundary scan testing

sysIO quick configuration

Density migration

Multiple density and package options

PQFP and fine pitch BGA packaging

Lead-free package options

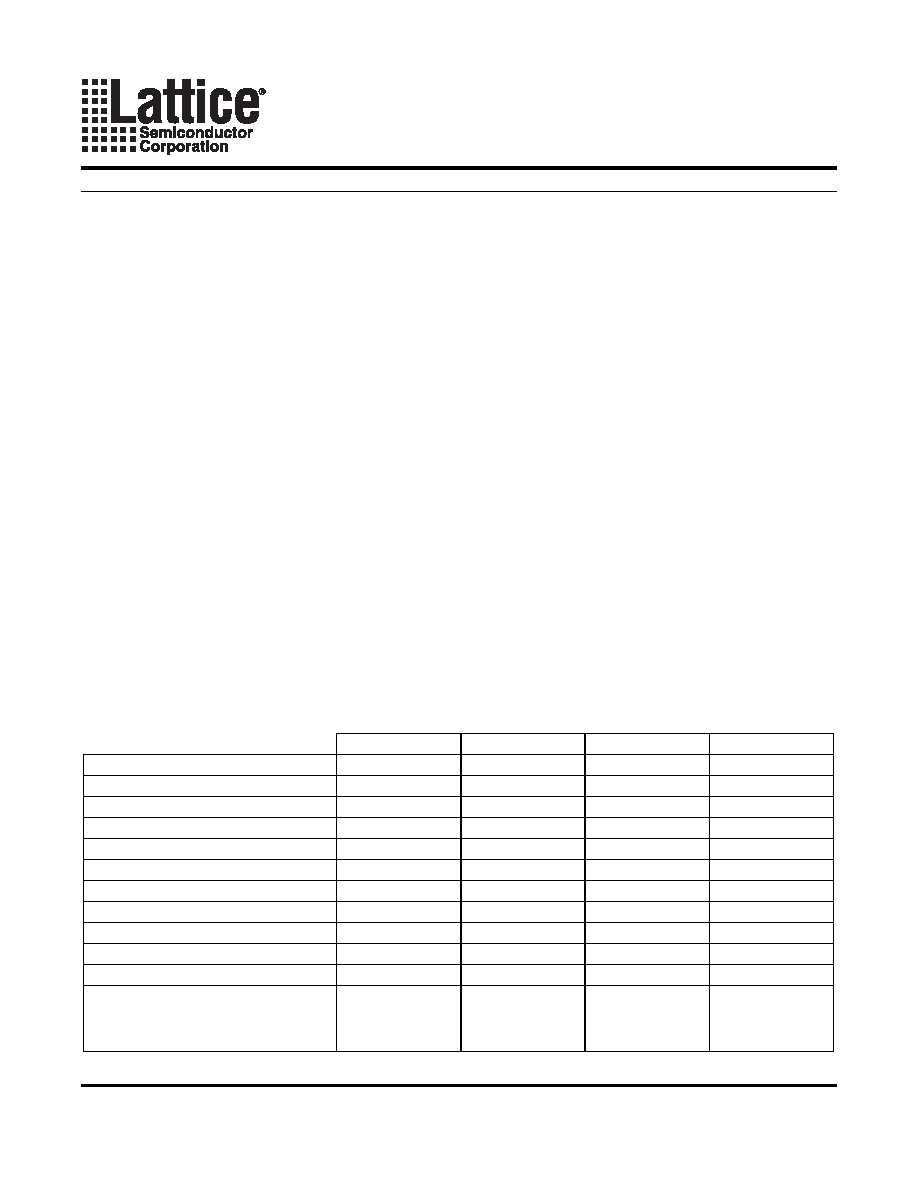

Table 1. ispXPLD 5000MX Family Selection Guide

ispXPLD 5256MX

ispXPLD 5512MX

ispXPLD 5768MX ispXPLD 51024MX

Macrocells

256

512

768

1,024

Multi-Function Blocks

8

16

24

32

Maximum RAM Bits

128K

256K

384K

512K

Maximum CAM Bits

48K

96K

144K

192K

sysCLOCK PLLs

2

tPD (Propagation Delay)

4.0ns

4.5ns

5.0ns

5.2ns

tS (Register Set-up Time)

2.2ns

2.8ns

3.0ns

tCO (Register Clock to Out Time)

2.8ns

3.0ns

3.2ns

3.7ns

fMAX (Maximum Operating Frequency)

300MHz

275MHz

250MHz

Functional Gates

75K

150K

225K

300K

I/Os

141

149/193/253

193/317

317/381

Packages

256 fpBGA

208 PQFP

256 fpBGA

484 fpBGA

256 fpBGA

484 fpBGA

672 fpBGA

相关PDF资料 |

PDF描述 |

|---|---|

| LC51024MV-75F484C | |

| LC5256MV-5F256I | |

| LC5512MV-45F256C | |

| LC5768MV-75F484I | |

| LC5768MV-75F256I | |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC5512MB-75F484C | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5512MB-75F484I | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM EXPANDED LOG RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LC5512MB-75F672C | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MB-75F672I | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

| LC5512MB-75FN208C | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:3.3V, 2.5V and 1.8V In-System Programmable eXpanded Programmable Logic Device XPLD⑩ Family |

发布紧急采购,3分钟左右您将得到回复。