- 您现在的位置:买卖IC网 > PDF目录30731 > LC72708E (SANYO SEMICONDUCTOR CO LTD) SPECIALTY CONSUMER CIRCUIT, PQFP44 PDF资料下载

参数资料

| 型号: | LC72708E |

| 厂商: | SANYO SEMICONDUCTOR CO LTD |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP44 |

| 封装: | QIP-44 |

| 文件页数: | 14/15页 |

| 文件大小: | 159K |

| 代理商: | LC72708E |

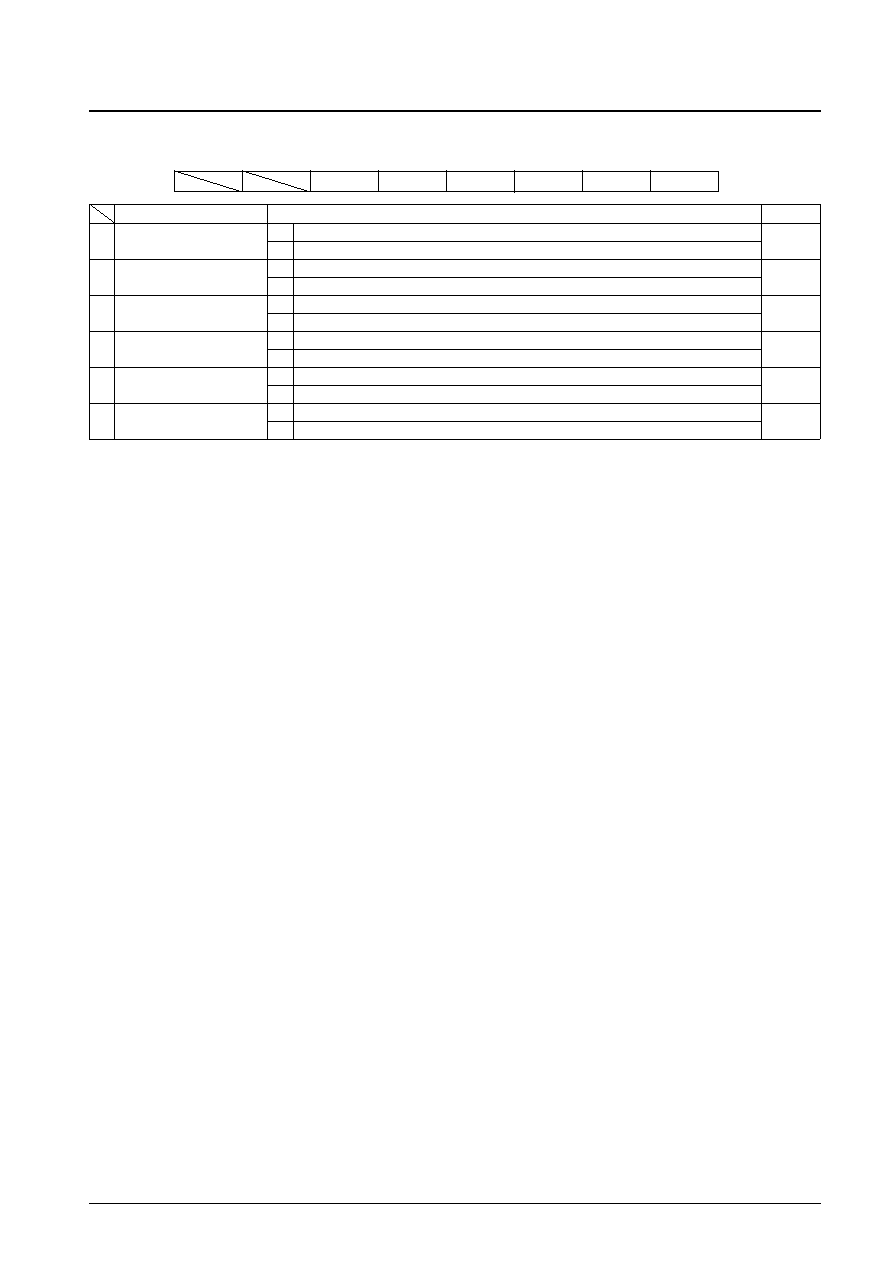

Control Register

Control register

Note: Bits 0 and 1 are unused.

No. 5875-8/15

LC72708E

VEC HALT

EC STOP

SYNC RST

INT MOVE

DO MOVE

CRC4 RST

0

1

2

3

4

5

6

7

Bit

Function

Initial value

2

VEC HALT

L

Vertical correction and second horizontal correction: enabled

L

(Vertical error correction stop)

H

Vertical correction and second horizontal correction: disabled

3

EC STOP

L

All functions operate

L

(Error correction stop)

H

Only the MSK detection and synchronization regeneration circuits operate

4

SYNC RST

L

Normal operation

L

(Synchronization block reset)

H

Only the synchronization circuit is reset

5

INT MOVE

L

Only the correction complete, layer 2 CRC complete, and data received while synchronized are output.

L

(INT type)

H

All data is output. (Operation identical to that of the LC72700)

6

DO MOVE

L

The high-level (high-impedance) state is held at times other than data output

L

(DO pin operation)

H

The DO pin changes with the INT pin. (Operation identical to that of the LC72700)

7

CRC4 RST

L

Normal operation

L

(Layer 4 CRC)

H

The layer 4 CRC circuit is reset to its initial state.

Detailed Descriptions

VEC HALT

Setting this flag stops all IC operations related to vertical and second horizontal correction. Data output is limited to

data following the first horizontal correction.

EC STOP

This flag stops all operations (including RAM access) related to error correction and all data output operations. While

all IC operations are stopped in standby mode, MSK demodulation, the synchronization circuit, the serial data input

circuit, and the layer 4 CRC circuit continue to operate in this mode.

SYNC RST

Clears the synchronization state and the synchronization protection state in the synchronization block and sets that

block to the unsynchronized state. This allows quick frame synchronization pull in when, during receiver tuning

operations, the frame period of the new reception data after station selection is displaced. While this flag is used for

initialization of synchronization related circuits, it does not initialize the number of allowed BIC errors, the block

synchronization forward and backward protection settings, and the registers of frame synchronization forward and

backward protection settings. During the synchronization block reset, the INT signal is not output and the DO pin

outputs a high level (high impedance). Since this flag is not automatically reset to 0, applications must send data again

to set it to 0.

INT MOVE

The data output by this IC is fully corrected, and only data received during both block and frame synchronization is

output. (The layer 2 CRC check is included.) This flag must be set to acquire all data in the same manner as the

LC72700.

DO MOVE

In the LC72700, the DO pin output was linked to and changed with the INT signal so that it could be used in place of

the INT CPU interrupt signal. Set this flag to use that function.

相关PDF资料 |

PDF描述 |

|---|---|

| LC72709E | SPECIALTY CONSUMER CIRCUIT, PQFP44 |

| LC72709W | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| LC72709E | SPECIALTY CONSUMER CIRCUIT, PQFP44 |

| LC72709W | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| LC72710LW | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC72709 | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:FM Multiplex Reception IC for Mobile Systems |

| LC72709E | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:FM Multiplex Reception IC for Mobile Systems |

| LC72709W | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:FM Multiplex Reception IC for Mobile Systems |

| LC72710 | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:Mobile FM Multiplex Broadcast DARC Receiver IC with On-Chip VICS Decoder |

| LC72710LW | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:Mobile FM Multiplex Broadcast DARC Receiver IC with On-Chip VICS Decoder |

发布紧急采购,3分钟左右您将得到回复。