- 您现在的位置:买卖IC网 > PDF目录30736 > LC78630E SPECIALTY CONSUMER CIRCUIT, PQFP80 PDF资料下载

参数资料

| 型号: | LC78630E |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| 封装: | QFP-80 |

| 文件页数: | 11/33页 |

| 文件大小: | 432K |

| 代理商: | LC78630E |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页

FSX is a 7.35 kHz frame synchronization signal generated by dividing the crystal clock. The error correction state for

each frame is output from EFLG. EFLG indicates the C1 correction state while FSX is high and the C2 correction

state while FSX is low. The playback OK/NG state can be easily determined from the number of high levels that

appear here.

Note: The FSX polarity is opposite in the LC78620 and LC7860 Series LSIs.

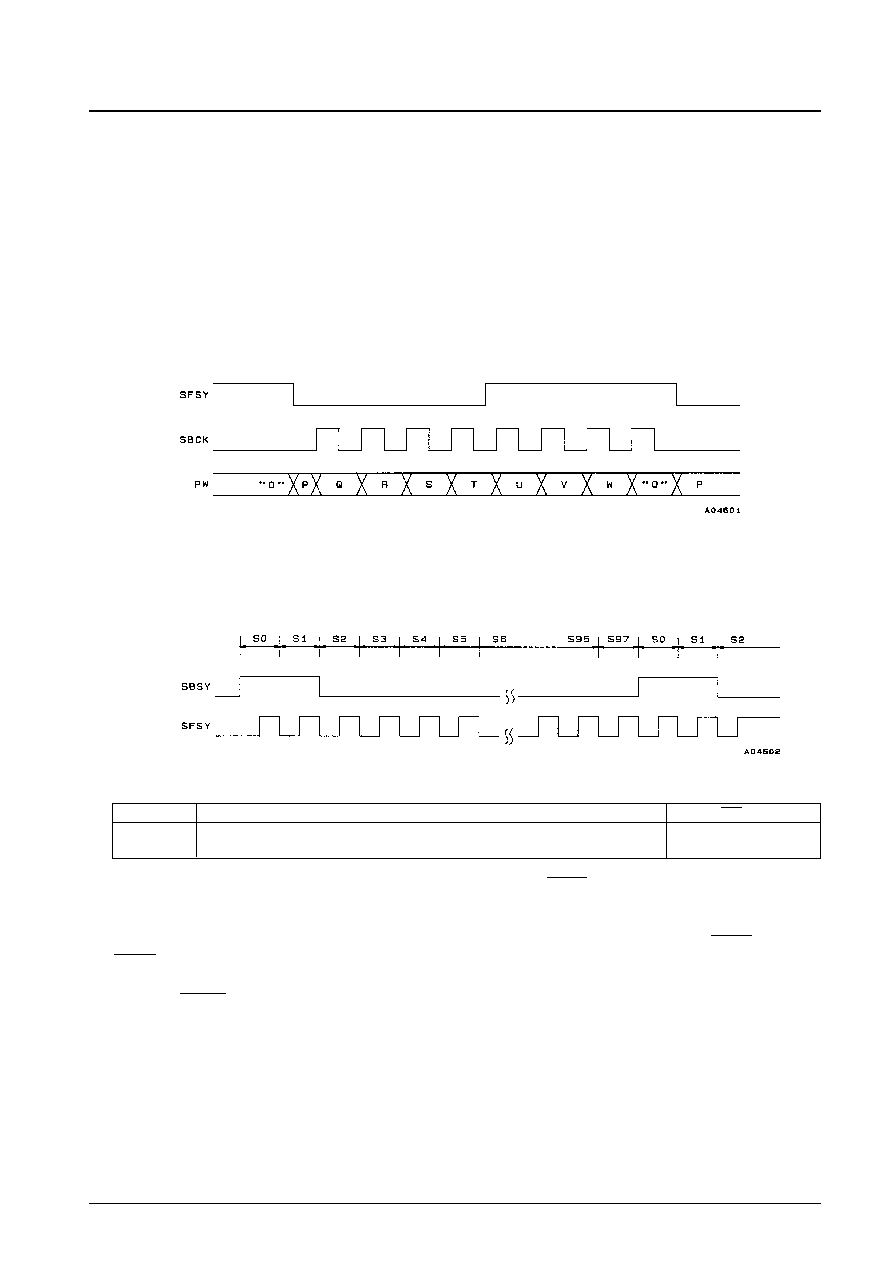

9. Subcode P, Q, and R to W output circuit; Pin 62: PW, pin 60: SBSY, pin 63: SFSY, pin 64: SBCK

PW is the subcode signal output pin, and all the codes, P, Q, and R to W can be read out by sending eight clocks to

the SBCK pin within 136 s after the fall of SFSY. The signal that appears on the PW pin changes on the rising edge

of SBCK. If a clock is not applied to SBCK, the P code will be output from PW. SFSY is a signal that is output for

each subcode frame cycle, and the falling edge of this signal indicates standby for the output of the subcode symbol

(P to W). Subcode data P is output on the fall of this signal.

SBSY is a signal output for each subcode block. This signal goes high for the S0 and S1 synchronizing signals. The

fall of this signal indicates the end of the subcode synchronizing signals and the start of the data in the subcode

block. (EIAJ format)

10. Subcode Q output circuit; Pin 67: WRQ, pin 68: RWC, pin 69: SQOUT, pin 71: CQCK, pin 78: CS

Subcode Q can be read from the SQOUT pin by applying a clock to the CQCK pin.

Of the eight bits in the subcode, the Q signal is used for song (track) access and display. The WRQ will be high only

if the data passed the CRC error check and the subcode Q format internal address is 1*. The control microprocessor

can read out data from SQOUT in the order shown below by detecting this high level and applying CQCK. When

CQCK is applied the DSP disables register update internally. The microprocessor should give update permission by

setting RWC high briefly after reading has completed. WRQ will fall to low at this time. Since the WRQ high period

is 11.2 ms, CQCK must be applied during the high period. Note that data is read out in an LSB first format.

Note: If RWC is set high by command while WRQ is high, WRQ will return to low and the SQOUT data will be

invalid.

Note: * This state will be ignored if an address free command is sent.

No. 5121-19/33

LC78630E

Code

Command

RES = low

$09

ADDRESS FREE

$89

ADDRESS 1

r

相关PDF资料 |

PDF描述 |

|---|---|

| LC78631E | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| LC78637E | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| LC78647NT | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| LC78648E | SPECIALTY CONSUMER CIRCUIT, PQFP80 |

| LC78681E | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC78631 | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:Compact Disk Player DSP |

| LC78631E | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:Compact Disk Player DSP |

| LC78632 | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:Compact Disk Player DSP |

| LC78632RE | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:Compact Disk Player DSP |

| LC78637E-E | 制造商:ON Semiconductor 功能描述: |

发布紧急采购,3分钟左右您将得到回复。