- 您现在的位置:买卖IC网 > PDF目录19788 > LCMXO1200C-5BN256C (Lattice Semiconductor Corporation)IC FPGA 1.2KLUTS 256CABGA PDF资料下载

参数资料

| 型号: | LCMXO1200C-5BN256C |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 40/88页 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1.2KLUTS 256CABGA |

| 标准包装: | 119 |

| 系列: | MachXO |

| 可编程类型: | 系统内可编程 |

| 最大延迟时间 tpd(1): | 3.6ns |

| 电压电源 - 内部: | 1.71 V ~ 3.465 V |

| 宏单元数: | 600 |

| 输入/输出数: | 211 |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 256-LFBGA,CSPBGA |

| 供应商设备封装: | 256-CABGA(14x14) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

�� �

�

DC� and� Switching� Characteristics�

�MachXO� Family� Data� Sheet�

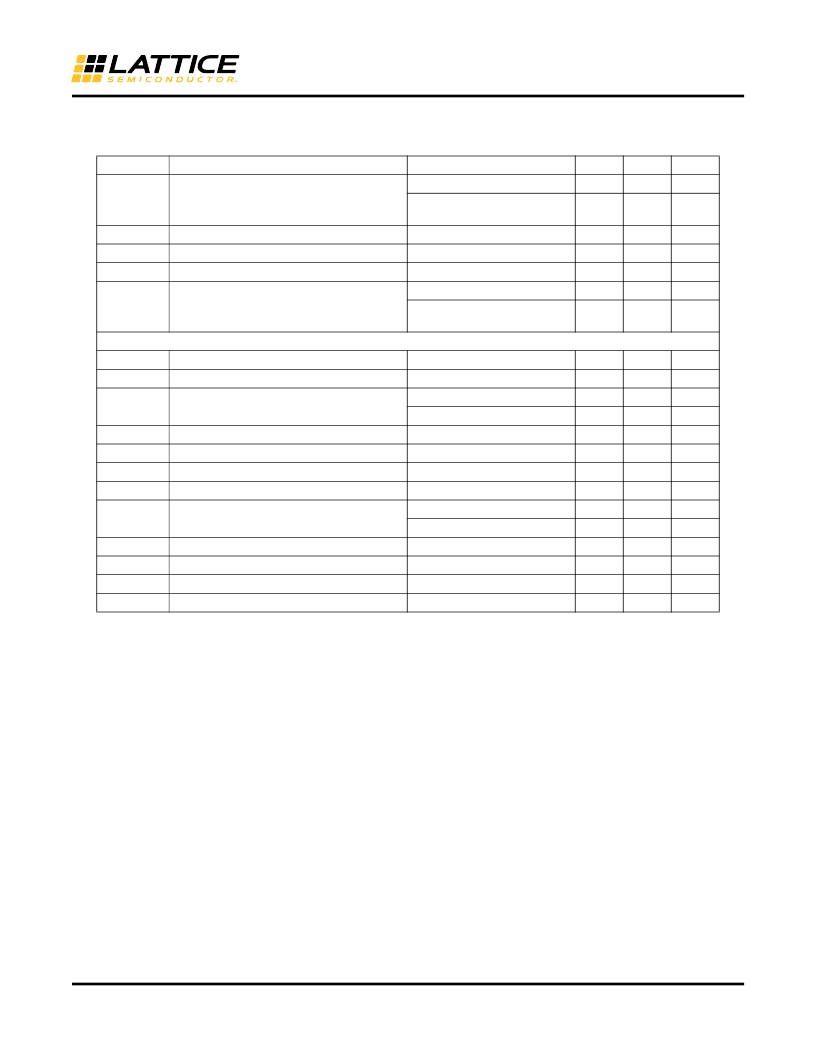

�sysCLOCK� PLL� Timing�

�Over� Recommended� Operating� Conditions�

�Parameter�

�Descriptions�

�Conditions�

�Min.�

�Max.�

�Units�

�25�

�420�

�MHz�

�f� IN�

�f� OUT�

�f� OUT2�

�f� VCO�

�Input� Clock� Frequency� (CLKI,� CLKFB)�

�Output� Clock� Frequency� (CLKOP,� CLKOS)�

�K-Divider� Output� Frequency� (CLKOK)�

�PLL� VCO� Frequency�

�Input� Divider� (M)� =� 1;�

�Feedback� Divider� (N)� <=� 4� 5,� 6�

�18�

�25�

�0.195�

�420�

�25�

�420�

�210�

�840�

�MHz�

�MHz�

�MHz�

�MHz�

�25�

�—�

�MHz�

�f� PFD�

�Phase� Detector� Input� Frequency�

�Input� Divider� (M)� =� 1;� ?�

�Feedback� Divider� (N)� <=� 4� 5,� 6�

�18�

�25�

�MHz�

�AC� Characteristics�

�t� PH�

�t� DT�

�4�

�t� OPJIT� 1�

�t� SK�

�t� W�

�t� LOCK� 2�

�t� PA�

�t� IPJIT�

�t� FBKDLY�

�t� HI�

�t� LO�

�t� RST�

�Output� Clock� Duty� Cycle�

�Output� Phase� Accuracy�

�Output� Clock� Period� Jitter�

�Input� Clock� to� Output� Clock� Skew�

�Output� Clock� Pulse� Width�

�PLL� Lock-in� Time�

�Programmable� Delay� Unit�

�Input� Clock� Period� Jitter�

�External� Feedback� Delay�

�Input� Clock� High� Time�

�Input� Clock� Low� Time�

�RST� Pulse� Width�

�Default� duty� cycle� selected� 3�

�f� OUT� >=� 100� MHz�

�f� OUT� <� 100� MHz�

�Divider� ratio� =� integer�

�At� 90%� or� 10%� 3�

�f� OUT� ?� 100� MHz�

�f� OUT� <� 100� MHz�

�90%� to� 90%�

�10%� to� 10%�

�45�

�—�

�—�

�—�

�—�

�1�

�—�

�100�

�—�

�—�

�—�

�0.5�

�0.5�

�10�

�55�

�0.05�

�+/-120�

�0.02�

�+/-200�

�—�

�150�

�450�

�+/-200�

�0.02�

�10�

�—�

�—�

�—�

�%�

�UI�

�ps�

�UIPP�

�ps�

�ns�

�μs�

�ps�

�ps�

�UI�

�ns�

�ns�

�ns�

�ns�

�1.�

�2.�

�3.�

�4.�

�5.�

�6.�

�Jitter� sample� is� taken� over� 10,000� samples� of� the� primary� PLL� output� with� a� clean� reference� clock.�

�Output� clock� is� valid� after� t� LOCK� for� PLL� reset� and� dynamic� delay� adjustment.�

�Using� LVDS� output� buffers.�

�CLKOS� as� compared� to� CLKOP� output.�

�When� using� an� input� frequency� less� than� 25� MHz� the� output� frequency� must� be� less� than� or� equal� to� 4� times� the� input� frequency.�

�The� on-chip� oscillator� can� be� used� to� provide� reference� clock� input� to� the� PLL� provided� the� output� frequency� restriction� for� clock�

�inputs� below� 25� MHz� are� followed.�

�Rev.� A� 0.19�

�3-14�

�相关PDF资料 |

PDF描述 |

|---|---|

| GBM24DSUS | CONN EDGECARD 48POS DIP .156 SLD |

| EEC06DREN | CONN EDGECARD 12POS .100 EYELET |

| LC4128ZC-75T100I | IC PLD 128MC 64I/O 7.5NS 100TQFP |

| LC4128ZC-42T100C | IC PLD 128MC 64I/O 4.2NS 100TQFP |

| RSC35DRYS-S734 | CONN EDGECARD 70POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LCMXO1200C-5FT256C | 功能描述:CPLD - 复杂可编程逻辑器件 1200 LUTs 211 IO 1.8 /2.5/3.3V -5 Spd RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LCMXO1200C-5FTN256C | 功能描述:CPLD - 复杂可编程逻辑器件 1200 LUTS 211 I/O RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LCMXO1200C-5M132C | 功能描述:CPLD - 复杂可编程逻辑器件 1200 LUTs 101 IO 1.8 /2.5/3.3V -5 Spd RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LCMXO1200C-5MN132C | 功能描述:CPLD - 复杂可编程逻辑器件 1200 LUTs 101 IO 1.8 /2.5/3.3V -5 Spd RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LCMXO1200C-5T100C | 功能描述:CPLD - 复杂可编程逻辑器件 1200 LUTs 73 IO 1.8/ 2.5/3.3V -5 Spd RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。