- 您现在的位置:买卖IC网 > PDF目录98001 > LMX2324ATM (NATIONAL SEMICONDUCTOR CORP) PLL FREQUENCY SYNTHESIZER, 2200 MHz, PDSO16 PDF资料下载

参数资料

| 型号: | LMX2324ATM |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 2200 MHz, PDSO16 |

| 封装: | TSSOP-16 |

| 文件页数: | 11/12页 |

| 文件大小: | 157K |

| 代理商: | LMX2324ATM |

2.0 Programming Description (Continued)

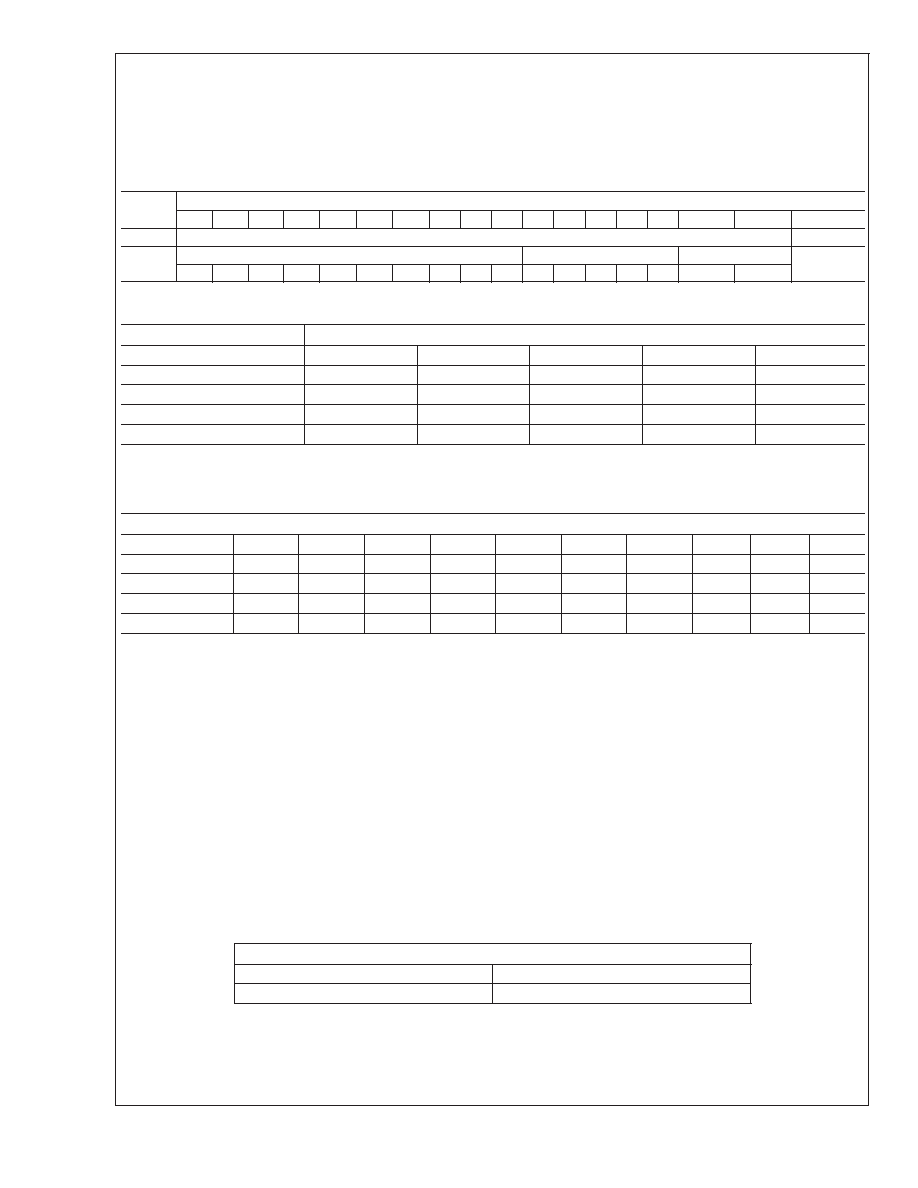

2.3 N REGISTER

If the address bit is LOW (ADDR=0) when LE is transitioned high, data is transferred from the 18-bit shift register into the 17-bit

N register. The N register consists of the 5-bit swallow counter (A counter), the 10-bit programmable counter (B counter) and the

control word. Serial data format is shown below in tables 2.3.1 and 2.3.2. The pulse swallow function which determines the divide

ratio is described in section 2.3.3. Data is clocked into the shift register MSB first.

MSB

SHIFT REGISTER BIT LOCATION

LSB

17

16

15

14

13

12

11

10

9

8

7654

3

2

1

0

Register

Data Field

ADDR Field

N

NB_CNTR[9:0]

NA_CNTR[4:0]

CTL_WORD[1:0]

0

N16

N15

N14

N13

N12

N11

N10

N9

N8

N7

N6

N5

N4

N3

N2

N1

N0

2.3.1 5-Bit Swallow Counter Divide Ratio (A Counter)

Swallow Count

NA_CNTR[4:0]

(A)

N6

N5

N4

N3

N2

0

00000

1

00001

31

11111

Notes: Swallow Counter Value: 0 to 31

NB_CNTR

≥ NA_CNTR

2.3.2 10-Bit Programmable Counter Divide Ratio (B Counter)

NB_CNTR[10:0]

Divide Ratio

N16

N15

N14

N13

N12

N11

N10

N9

N8

N7

3

0000000

0

1

4

0000000

1

0

1023

1111111

1

Notes: Divide ratio: 3 to 1,023 (Divide ratios less than 3 are prohibited)

NB_CNTR

≥ NA_CNTR

2.3.3 Pulse Swallow Function

The N divider counts such that it divides the VCO RF frequency by (P+1) A times, and then divides by P (B - A) times. The B value

(NB_CNTR) must be

≥ 3. The continuous divider ratio is from 992 to 32,767. Divider ratios less than 992 are achievable as long

as the binary counter value is greater than the swallow counter value (NB_CNTR

≥ NA_CNTR).

f

VCO =Nx(fOSC/R)

N=(P x B) + A

f

VCO:

Output frequency of external voltage controlled oscillator (VCO)

f

OSC:

Output frequency of the external reference frequency oscillator

R:

Preset divide ratio of binary 10-bit programmable reference counter (2 to 1023)

N:

Preset divide ratio of main 15-bit programmable integer N counter (992 to 32,767)

B:

Preset divide ratio of binary 10-bit programmable B counter (3 to 1023)

A:

Preset value of binary 5-bit swallow A counter (0

≤ A ≤ 31, A ≤ B)

P:

Preset modulus of dual modulus prescaler (P=32)

2.3.4 CTL_WORD

MSB

LSB

N1

N0

CNT_RST

PWDN

LMX2324A

www.national.com

8

相关PDF资料 |

PDF描述 |

|---|---|

| LMX2364TMX/NOPB | PLL FREQUENCY SYNTHESIZER, 2600 MHz, PDSO24 |

| LMX2372MDC | PLL FREQUENCY SYNTHESIZER, 1200 MHz, UUC |

| LMX2531LQ1500EX | PLL FREQUENCY SYNTHESIZER, 80 MHz, QCC36 |

| LMZ12003EXTTZX | SWITCHING REGULATOR, 1000 kHz SWITCHING FREQ-MAX, PSSO7 |

| LMZ12003EXTTZ | SWITCHING REGULATOR, 1000 kHz SWITCHING FREQ-MAX, PSSO7 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LMX2324ATMX | 制造商:NSC 制造商全称:National Semiconductor 功能描述:PLLatinum? 2.2 GHz Frequency Synthesizer for RF Personal Communications (SL163188) |

| LMX2324SLBX | 功能描述:IC FREQ SYNTH 2.0GHZ 16LAMINATE RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:PLLatinum™ 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| LMX2324TM | 功能描述:IC FREQ SYNTHESIZER 16-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:PLLatinum™ 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| LMX2324TMX | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Serial-Input Frequency Synthesizer |

| LMX2324TMX/NOPB | 功能描述:IC FREQ SYNTH 2.0GHZ 16-TSSOP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:PLLatinum™ 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。