- 您现在的位置:买卖IC网 > PDF目录44573 > LMX2330LTMX/NOPB (NATIONAL SEMICONDUCTOR CORP) PLL FREQUENCY SYNTHESIZER, 2500 MHz, PDSO20 PDF资料下载

参数资料

| 型号: | LMX2330LTMX/NOPB |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 2500 MHz, PDSO20 |

| 封装: | 0.173 INCH, TSSOP-20 |

| 文件页数: | 11/26页 |

| 文件大小: | 631K |

| 代理商: | LMX2330LTMX/NOPB |

Application Information

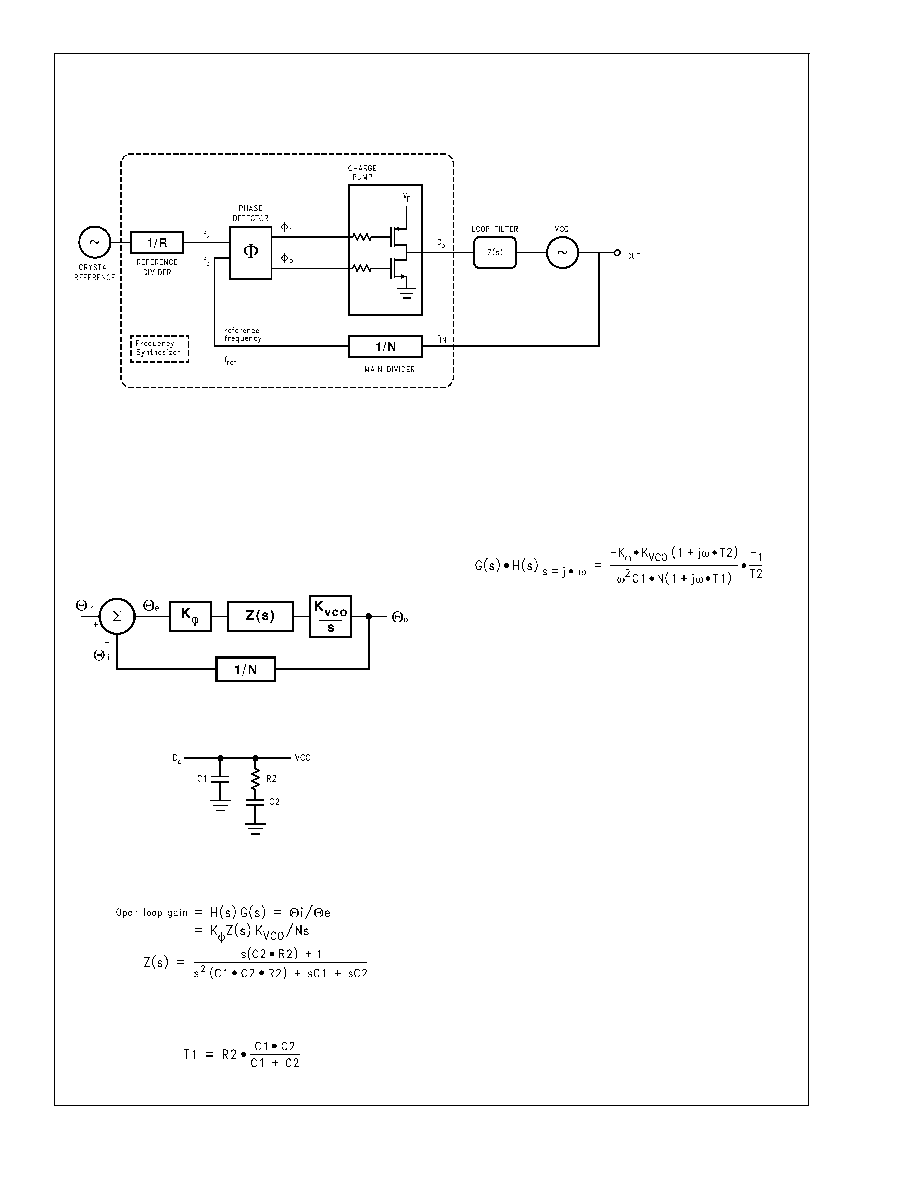

A block diagram of the basic phase locked loop is shown in

LOOP GAIN EQUATIONS

A linear control system model of the phase feedback for a

PLL in the locked state is shown in

Figure 2. The open loop

gain is the product of the phase comparator gain (K

φ), the

VCO gain (K

VCO/s), and the loop filter gain Z(s) divided by

the gain of the feedback counter modulus (N). The passive

loop filter configuration used is displayed in

Figure 3, while

the complex impedance of the filter is given in

(1)

The time constants which determine the pole and zero fre-

quencies of the filter transfer function can be defined as

(2)

and

T2=R2

C2

(3)

The 3rd order PLL Open Loop Gain can be calculated in

terms of frequency,

ω, the filter time constants T1 and T2,

and the design constants Kφ,KVCO, and N.

(4)

From

Equations (2), (3) we can see that the phase term will

be dependent on the single pole and zero such that the

phase margin is determined in

φ(ω) = tan 1 (ω T2) tan1 (ω T1) + 180

(5)

A plot of the magnitude and phase of G(s)H(s) for a stable

loop, is shown in

Figure 4 with a solid trace. The parameter

φ

p shows the amount of phase margin that exists at the point

the gain drops below zero (the cutoff frequency wp of the

loop). In a critically damped system, the amount of phase

margin would be approximately 45 degrees.

If we were now to redefine the cut off frequency, wp’, as

double the frequency which gave us our original loop band-

width, wp, the loop response time would be approximately

halved. Because the filter attenuation at the comparison

frequency also diminishes, the spurs would have increased

by approximately 6 dB. In the proposed Fastlock scheme,

the higher spur levels and wider loop filter conditions would

exist only during the initial lock-on phase — just long enough

to reap the benefits of locking faster. The objective would be

to open up the loop bandwidth but not introduce any addi-

tional complications or compromises related to our original

design criteria. We would ideally like to momentarily shift the

curve of

Figure 4 over to a different cutoff frequency, illus-

trated by the dotted line, without affecting the relative open

loop gain and phase relationships. To maintain the same

gain/phase relationship at twice the original cutoff frequency,

other terms in the gain and phase

Equation (4) and Equation

(5) will have to compensate by the corresponding “1/w” or

“1/w

2” factor. Examination of equations Equations (2), (3)

and

Equation (5) indicates the damping resistor variable R2

could be chosen to compensate the “w”’ terms for the phase

01280614

FIGURE 1. Basic Charge Pump Phase Locked Loop

01280615

FIGURE 2. PLL Linear Model

01280616

FIGURE 3. Passive Loop Filter

LMX2330L/LMX2331L/LMX2332L

www.national.com

19

相关PDF资料 |

PDF描述 |

|---|---|

| LMX2330LMWC | PLL FREQUENCY SYNTHESIZER, 2500 MHz, UUC |

| LMX2330LMDC | PLL FREQUENCY SYNTHESIZER, 2500 MHz, UUC |

| LMX2330LTM/NOPB | PLL FREQUENCY SYNTHESIZER, 2500 MHz, PDSO20 |

| LMX2331LTMX/NOPB | PLL FREQUENCY SYNTHESIZER, 2000 MHz, PDSO20 |

| LMX2332LTM/NOPB | PLL FREQUENCY SYNTHESIZER, 1200 MHz, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LMX2330TM | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Serial-Input Frequency Synthesizer |

| LMX2330U | 制造商:NSC 制造商全称:National Semiconductor 功能描述:PLLatinum Ultra Low Power Dual Frequency Synthesizer for RF Personal Communications |

| LMX2330USLBX | 功能描述:IC FREQ SYNTH DUAL 24LAMINATECSP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:PLLatinum™ 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| LMX2330USLEX/NOPB | 功能描述:IC FREQ SYNTH DUAL 20LAMUTCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:PLLatinum™ 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| LMX2330UTM | 功能描述:IC FREQ SYNTHESIZER DUAL 20TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:PLLatinum™ 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。