- 您现在的位置:买卖IC网 > PDF目录44574 > LMX2370TM/NOPB (NATIONAL SEMICONDUCTOR CORP) PLL FREQUENCY SYNTHESIZER, 2500 MHz, PDSO20 PDF资料下载

参数资料

| 型号: | LMX2370TM/NOPB |

| 厂商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 2500 MHz, PDSO20 |

| 封装: | PLASTIC, TSSOP-20 |

| 文件页数: | 8/25页 |

| 文件大小: | 577K |

| 代理商: | LMX2370TM/NOPB |

2.0 Programming Description (Continued)

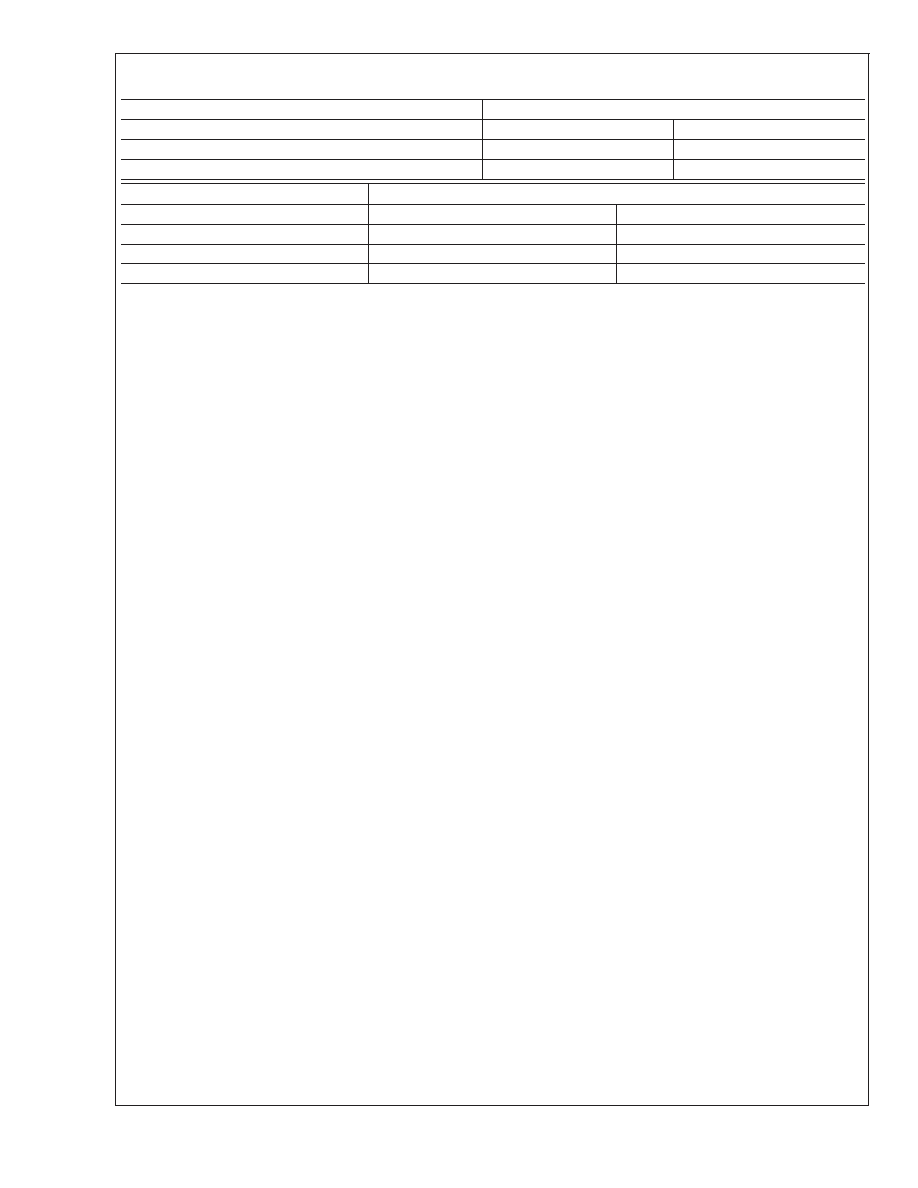

Prescaler Value

P_Main, (Main_N18) or P_Aux (Aux_N18)

2.5 GHz PLL

1.2 GHz PLL

0

16/17

8/9

1

32/33

16/17

Allowable Prescaler Values

PLL Input Frequency

2.5 GHz PLL

1.2 GHz PLL

f

IN > 1.2 GHz

32/33

NA

550 < f

IN < 1200 MHz

16/17 or 32/33

16/17

f

IN < 550 MHz

16/17 or 32/33

8/9 or 16/17

2.3.5.1 Pulse Swallow Function

f

VCO = [(P xB)+ A]xfOSC/R

f

VCO: Output frequency of external voltage controlled oscillator (VCO)

B:

Preset divide ratio of binary 13-bit programmable counter (3 to 8191)

A:

Preset divide ratio of binary 5-bit swallow counter

0

≤ A ≤ 31 {P=32}

0

≤ A ≤ 15 {P=16}

0

≤ A ≤ 7 {P=8}

A

≤ B

f

OSC: Output frequency of the external reference frequency oscillator

R:

Preset divide ratio of binary 15-bit programmable reference counter (3 to 32767)

P:

Preset modulus of dual modulus prescaler (P = 8, 16, or 32)

2.3.6 PLL Power Down Control (Aux_PWDN, Main_PWDN)

The Aux_PWDN (Aux_N19) and Main_PWDN (Main_N19) bits are used to power down either the Main or Auxiliary PLL’s charge

pump portion, or the entire PLL block depending on the setting of the respective charge pump TRI-STATE bit (Aux_CP

o_TRI or

Main_CP

o_TRI) in the R_CNTR register. The power-down mechanism is described below. The R and N counters for each

respective PLL are disabled and held at reset during the synchronous and asynchronous power down modes. This will allow a

smooth acquisition of the Main RF signal when the oscillator input buffer is still active (Auxiliary loop powered up) and vice versa.

Upon powering up, both R and N counters will start at the “zero” state, and the relationship between R and N will not be random.

Synchronous Power Down Mode

One of the PLL loops can be synchronously powered down by first setting the respective loop’s TRI-STATE mode bit LOW (R17

= 0) and then asserting its power down mode bit (N19 = 1). The power down function is gated by the charge pump. Once the

power down program bits Aux_PWDN (Aux_N19) and Main_PWDN (Main_N19) and TRI-STATE bits Aux_CP

o_TRI (Aux_R17)

or Main_CP

o_TRI (Main_R17) are loaded, the part will go into power down mode upon the completion of a charge pump pulse

event.

Asynchronous Power Down Mode

One of the PLL loops can be asynchronously powered down by first setting the respective loop’s TRI-STATE mode bit HI (R17

= 1) and then asserting its power down mode bit (N19 = 1). The power down function is NOT gated by the charge pump. Once

the power down program bits Aux_PWDN (Aux_N19) and Main_PWDN (Main_N19) and its respective TRI-STATE bit Aux_CP

o-

_TRI (Aux_R17) or Main_CP

o_TRI (Main_R17) are loaded, the part will go into power down mode immediately.

LMX2370

www.national.com

16

相关PDF资料 |

PDF描述 |

|---|---|

| LMX2512LQX0967/NOPB | PLL FREQUENCY SYNTHESIZER, 19.68 MHz, QCC28 |

| LMX2515LQX0701/NOPB | PLL FREQUENCY SYNTHESIZER, 26 MHz, QCC28 |

| LMX2525LQ1321/NOPB | PLL FREQUENCY SYNTHESIZER, 26 MHz, QCC24 |

| LMZ12001EXTTZE | SWITCHING REGULATOR, 1000 kHz SWITCHING FREQ-MAX, PSSO7 |

| LMZ12001TZE-ADJ | SWITCHING REGULATOR, 1000 kHz SWITCHING FREQ-MAX, PSSO7 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LMX2370TMX | 功能描述:IC FREQ SYNTH DL 2.5GHZ 20-TSSOP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:PLLatinum™ 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

| LMX2370TMX/NOPB | 制造商:Texas Instruments 功能描述:PLL Frequency Synthesizer Dual 45MHz to 2500MHz 20-Pin TSSOP T/R |

| LMX2371 | 制造商:未知厂家 制造商全称:未知厂家 功能描述: |

| LMX2371 WAF | 制造商:Texas Instruments 功能描述: |

| LMX2371SLBX | 功能描述:IC FREQ SYNTH DUAL 24LAMINATECSP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:PLLatinum™ 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:* |

发布紧急采购,3分钟左右您将得到回复。