- 您现在的位置:买卖IC网 > PDF目录19392 > LSM2-T/10-W3-C (Murata Power Solutions Inc)CONV DC/DC 33W 10A 5V SMD PDF资料下载

参数资料

| 型号: | LSM2-T/10-W3-C |

| 厂商: | Murata Power Solutions Inc |

| 文件页数: | 14/17页 |

| 文件大小: | 0K |

| 描述: | CONV DC/DC 33W 10A 5V SMD |

| 标准包装: | 1 |

| 系列: | LSM2 |

| 类型: | 非隔离(POL) |

| 输出数: | 1 |

| 电压 - 输入(最小): | 2.4V |

| 电压 - 输入(最大): | 5.5V |

| Voltage - Output 1: | 0.75 ~ 3.3 V |

| 电流 - 输出(最大): | 10A |

| 电源(瓦) - 制造商系列: | 33W |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-DIP SMD 模块 |

| 尺寸/尺寸: | 1.30" L x 0.53" W x 0.34" H(33.0mm x 13.5mm x 8.6mm) |

| 包装: | 标准包装 |

| 工作温度: | -40°C ~ 85°C |

| 效率: | 95.5% |

| 电源(瓦特)- 最大: | 33W |

| 产品目录页面: | 2719 (CN2011-ZH PDF) |

| 其它名称: | 811-1785-6 |

�� �

�

�

�LSM2� Series�

�Single� Output,� Non-Isolated�

�Selectable-Output� POL� DC/DC� Converters�

�Operation�

�To� use� the� Sequence� pin� after� power� start-up� stabilizes,� apply� a� rising� external�

�voltage� to� the� Sequence� input.� As� the� voltage� rises,� the� output� voltage� will�

�track� the� Sequence� input� (gain� =� 1).� The� output� voltage� will� stop� rising� when� it�

�reaches� the� normal� set� point� for� the� converter.� The� Sequence� input� may� option-�

�ally� continue� to� rise� without� any� effect� on� the� output.� Keep� the� Sequence� input�

�voltage� below� the� converter’s� input� supply� voltage.�

�Use� a� similar� strategy� on� power� down.� The� output� voltage� will� stay� constant�

�until� the� Sequence� input� falls� below� the� set� point.�

�Any� strategy� may� be� used� to� deliver� the� power� up/down� ramps.� The� circuits�

�below� show� simple� RC� networks� but� you� may� also� use� operational� ampli?ers,�

�D/A� converters,� etc.�

�Circuits�

�The� circuits� shown� in� Figures� 14� through� 16� introduce� several� concepts� when�

�using� these� Sequencing� controls� on� Point-of-Load� (POL)� converters.� These�

�circuits� are� only� for� reference� and� are� not� intended� as� ?nal� designs� ready� for�

�your� application.� Also,� numerous� connections� are� omitted� for� clarity.�

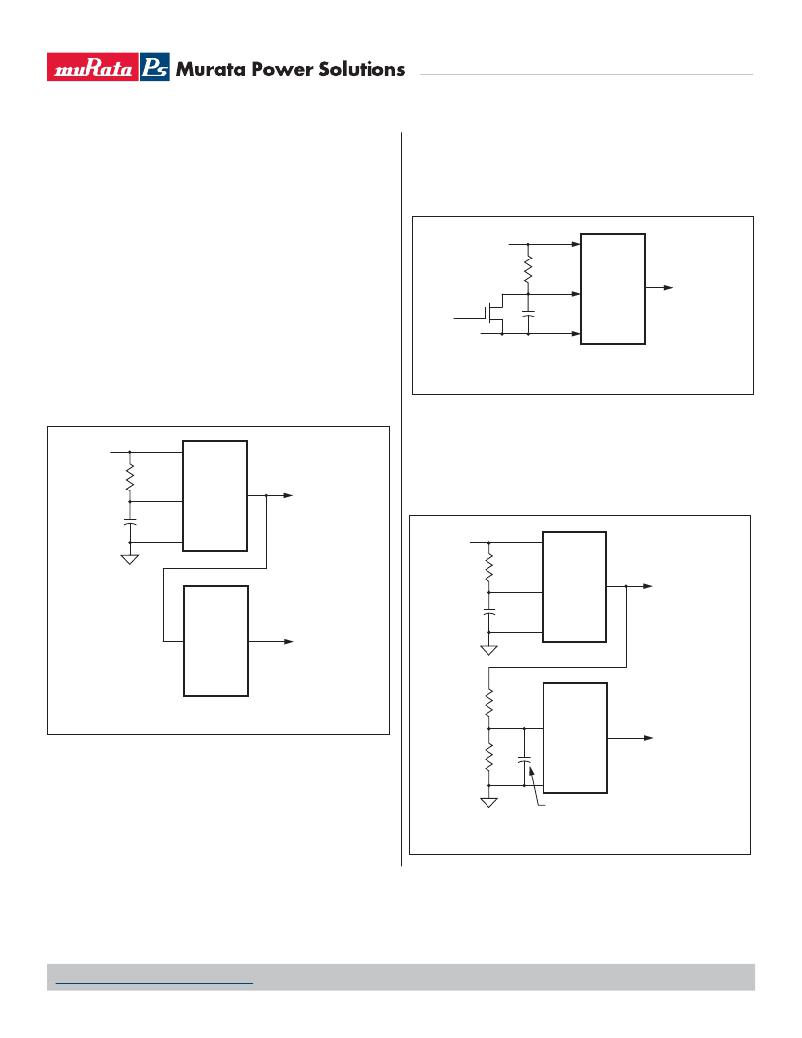

�Figure� 15� shows� a� single� POL� and� the� same� RC� network.� However,� we� have�

�added� a� FET� at� Q1� as� an� up/down� control.� When� V� IN� power� is� applied� to� the�

�POL,� Q1� is� biased� on,� shorting� out� the� Sequence� pin.� When� Q1’s� gate� is� biased�

�off,� R1� charges� C1� and� the� POL’s� output� ramps� up� at� the� R1-C1� slew� rate.� Note:�

�Q1’s� gate� would� typically� be� controlled� from� some� external� digital� logic.�

�Figure� 15.� Self-Ramping� Power� Up�

�If� you� wish� to� have� a� ramped� power� down� (rather� than� a� step� down),� add� a�

�small� resistor� in� series� with� Q1’s� drain.�

�Figure� 16� shows� both� a� RC� ramp� on� Master� POL� A� and� a� proportional� track-�

�ing� divider� (R2� and� R3)� on� POL� B.� We� have� also� added� an� optional� very� small�

�noise� ?lter� cap� at� C2.� Figure� 16’s� circuit� corresponds� roughly� to� Figure� 11’s�

�timing� for� power� up.�

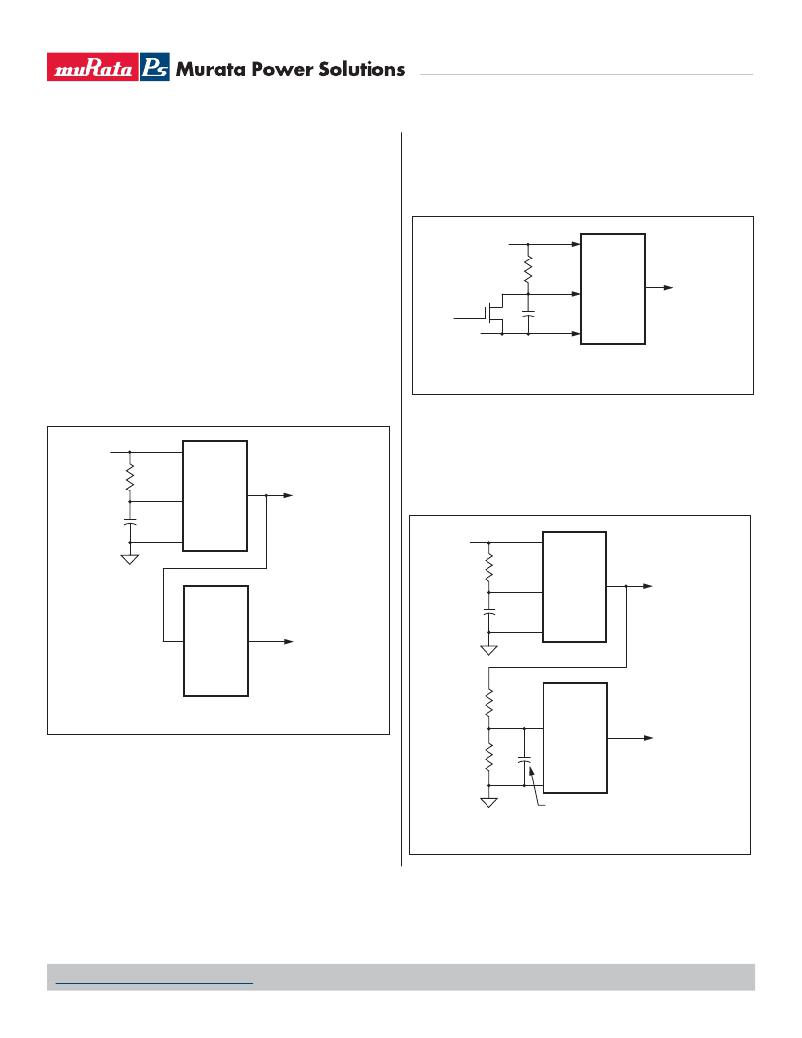

�Figure� 14.� Wiring� for� Simultaneous� Phasing�

�Figure� 14� shows� a� basic� Master� (POL� A)� and� Slave� (POL� B)� connected� so� the�

�POL� B� ramps� up� identically� to� POL� A� as� shown� in� timing� diagram,� Figure� 10.� RC�

�network� R1� and� C1� charge� up� at� a� rate� set� by� the� R1-C1� time� constant,� giving�

�a� roughly� linear� ramp.� As� POL� A� reaches� 3.3V� OUT� (the� setpoint� of� POL� B),� POL�

�B� will� stop� rising.� POL� A� then� continues� rising� until� it� reaches� 5V.� R1� should� be�

�signi?cantly� smaller� than� the� internal� bias� current� resistor� from� the� Sequence�

�pin.� Start� with� a� 20k� ??� value.� We� assume� that� the� critical� phase� is� only� on�

�Figure� 16.� Proportional� Phasing�

�power� up� therefore� there� is� no� provision� for� ramped� power� down.�

�www.murata-ps.com/support�

�M� D� C_LSM2� Series.C01� Δ� Page� 14� of� 17�

�相关PDF资料 |

PDF描述 |

|---|---|

| EEC18DRXN | CONN EDGECARD 36POS DIP .100 SLD |

| EBC06DRXI | CONN EDGECARD 12POS DIP .100 SLD |

| ADSP-BF524KBCZ-4C2 | IC DSP CTRLR 400MHZ 289CSPBGA |

| TAP226M020CRW | CAP TANT 22UF 20V 20% RADIAL |

| EEC18DRXH | CONN EDGECARD 36POS DIP .100 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LSM2-T30-D12 | 制造商:MURATA 制造商全称:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

| LSM2-T-30-D12-C | 制造商:MURATA 制造商全称:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

| LSM2-T30-D12-C | 制造商:MURATA 制造商全称:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

| LSM2-T-30-D12R-C | 制造商:MURATA 制造商全称:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

| LSM2-T30-D12R-C | 制造商:MURATA 制造商全称:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

发布紧急采购,3分钟左右您将得到回复。