- 您现在的位置:买卖IC网 > Datasheet目录867 > LSM2-T/16-D12N-C (Murata Power Solutions Inc)CONV DC/DC 80W 16A 12V SMD Datasheet资料下载

参数资料

| 型号: | LSM2-T/16-D12N-C |

| 厂商: | Murata Power Solutions Inc |

| 文件页数: | 13/17页 |

| 文件大小: | 0K |

| 描述: | CONV DC/DC 80W 16A 12V SMD |

| 标准包装: | 1 |

| 系列: | LSM2 |

| 类型: | 非隔离(POL) |

| 输出数: | 1 |

| 电压 - 输入(最小): | 8.3V |

| 电压 - 输入(最大): | 13.2V |

| Voltage - Output 1: | 0.75 ~ 5 V |

| 电流 - 输出(最大): | 16A |

| 电源(瓦) - 制造商系列: | 80W |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 8-DIP SMD 模块 |

| 尺寸/尺寸: | 1.30" L x 0.53" W x 0.34" H(33.0mm x 13.5mm x 8.6mm) |

| 包装: | 标准包装 |

| 工作温度: | -40°C ~ 85°C |

| 效率: | 94% |

| 电源(瓦特)- 最大: | 80W |

| 其它名称: | 811-1791-6 |

�� �

�

�

�LSM2� Series�

�Single� Output,� Non-Isolated�

�Selectable-Output� POL� DC/DC� Converters�

�Power� Phasing� Architectures�

�Observe� the� simpli?ed� timing� diagrams� below.� There� are� many� possible� power�

�phasing� architectures� and� these� are� just� some� examples� to� help� you� analyze�

�your� system.� Each� application� will� be� different.� Multiple� output� voltages� may�

�require� more� complex� timing� than� that� shown� here.�

�These� diagrams� illustrate� the� time� and� slew� rate� relationship� between� two�

�typical� power� output� voltages.� Generally� the� Master� will� be� a� primary� power�

�voltage� in� the� system� which� must� be� present� ?rst� or� coincident� with� any�

�Slave� power� voltages.� The� Master� output� voltage� is� connected� to� the� Slave’s�

�Sequence� input,� either� by� a� voltage� divider,� divider-plus-capacitor� or� some�

�other� method.� Several� standard� sequencing� architectures� are� prevalent.� They�

�are� concerned� with� three� factors:�

�?� The� time� relationship� between� the� Master� and� Slave� voltages�

�?� The� voltage� difference� relationship� between� the� Master� and� Slave�

�?� The� voltage� slew� rate� (ramp� slope)� of� each� converter’s� output.�

�For� most� systems,� the� time� relationship� is� the� dominant� factor.� The� voltage�

�difference� relationship� is� important� for� systems� very� concerned� about� possible�

�latchup� of� programmable� devices� or� overdriving� ESD� diodes.� Lower� slew� rates�

�avoid� overcurrent� shutdown� during� bypass� cap� charge-up.�

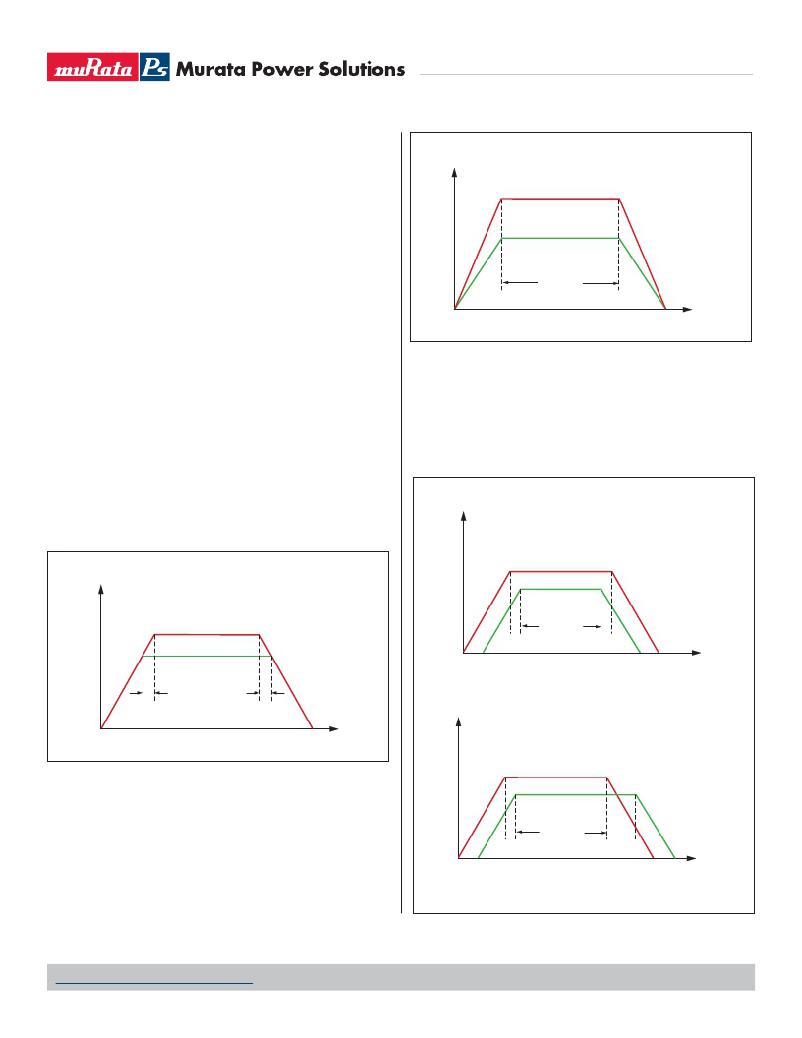

�Figure� 11.� Proportional� or� Ratiometric� Phasing� (Identical� V� OUT� Time)�

�Figures� 12� and� 13� show� both� delayed� start� up� and� delayed� ?nal� voltages�

�for� two� converters.� Figure� 12� is� called� “Inclusive”� because� the� later� starting�

�POL� ?nishes� inside� the� earlier� POL.� The� timing� in� Figure� 12� is� more� easily� built�

�using� a� combined� digital� sequence� controller� and� the� Sequence/Track� pin.�

�Figure� 13� is� the� same� strategy� as� Figure� 12� but� with� an� “exclusive”� timing�

�relationship� staggered� approximately� the� same� at� power-up� and� power-down.�

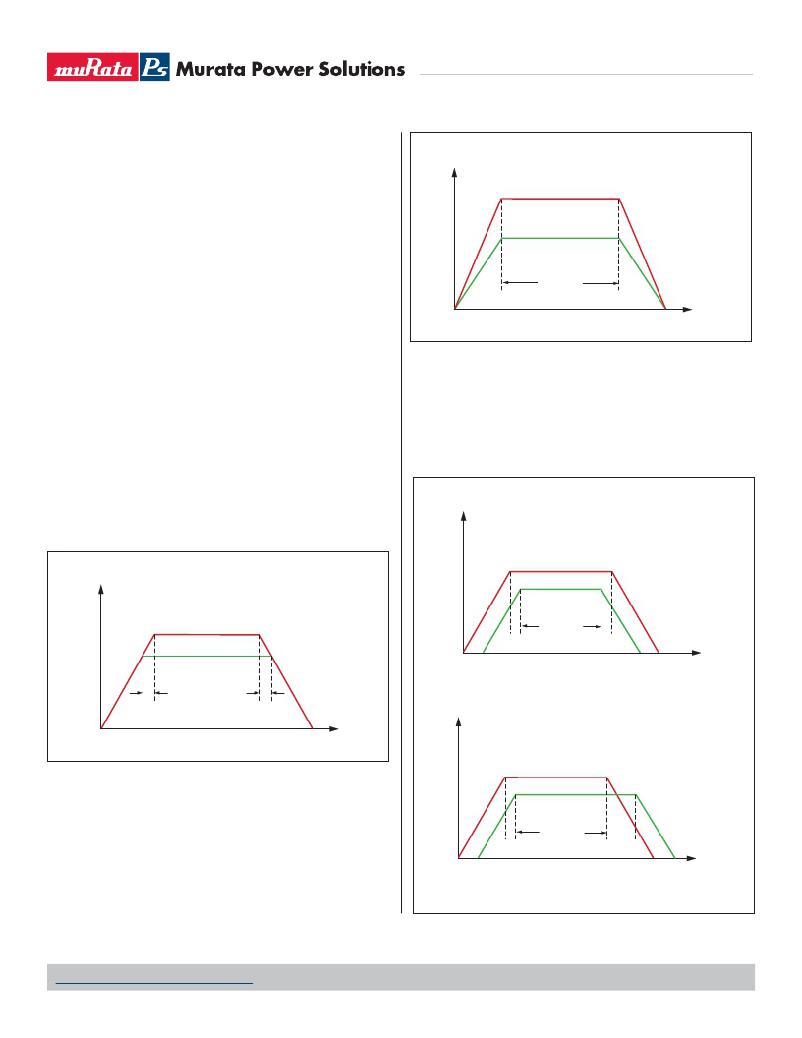

�In� Figure� 10,� two� POL’s� ramp� up� at� the� same� rate� until� they� reach� their�

�different� respective� ?nal� set� point� voltages.� During� the� ramp,� their� voltages�

�are� nearly� identical.� This� avoids� problems� with� large� currents� ?owing� between�

�logic� systems� which� are� not� initialized� yet.� Since� both� end� voltages� are� differ-�

�ent,� each� converter� reaches� it’s� setpoint� voltage� at� a� different� time.�

�Figure� 12.� Staggered� or� Sequential� Phasing—Inclusive� (Fixed� Delays)�

�Figure� 10.� Coincident� or� Simultaneous� Phasing� (Identical� Slew� Rates)�

�Figure� 11� shows� two� POL’s� with� different� slew� rates� in� order� to� reach� differ-�

�ing� ?nal� voltages� at� about� the� same� time.�

�Figure� 13.� Staggered� or� Sequential� Phasing—Exclusive�

�(Fixed� Cascaded� Delays)�

�www.murata-ps.com/support�

�M� D� C_LSM2� Series.C01� Δ� Page� 13� of� 17�

�相关PDF资料 |

PDF描述 |

|---|---|

| LSM2-T/30-D12R-C | CONV DC/DC 125W 30A 12V SMD |

| LSN-T/10-D12N-C | CONV DC/DC 10A 0.75-5.25V SIP |

| LSN-T/16-D12-C | CONV DC/DC 80W 16A 0.75-5V SIP |

| LSN-T/16-W3-C | CONV DC/DC 16A .75-3.3V SIP |

| LSN2-T/16-W3N-C | CONV DC/DC 52.8W 16A.75-3.3V SIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LSM2-T30-D12 | 制造商:MURATA 制造商全称:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

| LSM2-T-30-D12-C | 制造商:MURATA 制造商全称:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

| LSM2-T30-D12-C | 制造商:MURATA 制造商全称:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

| LSM2-T-30-D12R-C | 制造商:MURATA 制造商全称:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

| LSM2-T30-D12R-C | 制造商:MURATA 制造商全称:Murata Manufacturing Co., Ltd. 功能描述:DOSA-SMT, 30A POL DC/DC Converters |

发布紧急采购,3分钟左右您将得到回复。