- 您现在的位置:买卖IC网 > PDF目录11021 > LTC1164-7CSW (Linear Technology)IC FILTR 8TH ORDR LOWPASS 16SOIC PDF资料下载

参数资料

| 型号: | LTC1164-7CSW |

| 厂商: | Linear Technology |

| 文件页数: | 16/16页 |

| 文件大小: | 0K |

| 描述: | IC FILTR 8TH ORDR LOWPASS 16SOIC |

| 标准包装: | 47 |

| 滤波器类型: | 线性相位,低通开关电容器 |

| 频率 - 截止或中心: | 100kHz |

| 滤波器数: | 1 |

| 滤波器阶数: | 8th |

| 电源电压: | 4.75 V ~ 16 V,±2.375 V ~ 8 V |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SOIC(0.295",7.50mm 宽) |

| 供应商设备封装: | 16-SOIC |

| 包装: | 管件 |

| 其它名称: | LTC1164-7CS |

9

LTC1164-7

11647fb

PI FU CTIO S

U

UU

External Connection (Pins 7, 14): Pins 7 and 14 should be

connected together. In a printed circuit board the connec-

tion should be done under the IC package through a short

trace surrounded by the analog ground plane.

Ratio Input (Pin 10): The DC level at this pin determines

the ratio of the clock frequency to the cutoff frequency of

the filter. Pin 10 at V

+ gives a 50:1 ratio and pin 10 at V–

gives a 100:1 ratio. For single supply operation the ratio is

50:1 when Pin 10 is at V

+ and 100:1 when Pin 10 is at

ground. When Pin 10 is not tied to ground, it should be

bypassed to analog ground with a 0.1

F capacitor. If the

DC level at Pin 10 is switched mechanically or electrically

at slew rates greater than 1V/

s while the device is

operating, a 10k resistor should be connected between pin

10 and the DC source.

Clock Input (Pin 11): Any TTL or CMOS clock source with

a square-wave output and 50% duty cycle (

±10%) is an

adequate clock source for the device. The power supply for

the clock source should not be the filter’s power supply.

The analog ground for the filter should be connected to

clock’s ground at a single point only. Table 7 shows the

clock’s low and high level threshold values for dual or

single supply operation. A pulse generator can be used as

a clock source provided the high level ON time is greater

than 0.5

s. Sine waves are not recommended for clock

input frequencies less than 100kHz, since excessively

slow clock rise or fall times generate internal clock jitter

(maximum clock rise or fall time

≤ 1s). The clock signal

should be routed from the right side of the IC package and

perpendicular to it to avoid coupling to any input or output

analog signal path. A 1k resistor between clock source and

Pin 11 will slow down the rise and fall times of the clock to

further reduce charge coupling (Figures 2 and 3).

NC (Pins 1, 8, 13): Pins 1, 8 and 13 are not connected to

any internal circuit point on the device and should be

preferably tied to analog ground.

Filter Input (Pin 2): The input pin is connected internally

through a 50k resistor tied to the inverting input of an op

amp.

Analog GND (Pins 3, 5): The filter performance depends

on the quality of the analog signal ground. For either dual

or single supply operation, an analog ground plane sur-

rounding the package is recommended. The analog ground

plane should be connected to any digital ground at a single

point. For dual supply operation, Pins 3 and 5 should be

connected to the analog ground plane. For single supply

operation, Pins 3 and 5 should be biased at 1/2 supply and

should be bypassed to the analog ground plane with at

least a 1

F capacitor (Figure 3). For single 5V operation at

the highest fCLK of 2MHz, Pins 3 and 5 should be biased at

2V. This minimizes passband gain and phase variations.

Power Supply (Pins 4, 12): The V

+ (pin 4) and the V – (Pin

12) should each be bypassed with a 0.1

F capacitor to an

adequate analog ground. The filter’s power supplies should

be isolated from other digital or high voltage analog

supplies. A low noise linear supply is recommended.

Using a switching power supply will lower the signal-to-

noise ratio of the filter. The supply during power-up should

have a slew rate less than 1V/

s.WhenV+isappliedbefore

V

– and V– is allowed to go above ground, a signal diode

should clamp V

– to prevent latch-up. Figures 2 and 3 show

typical connections for dual and single supply operation.

Filter Output (Pins 6, 9): Pin 6 is an intermediate filter

output providing an unspecified 6th order lowpass filter.

Pin 6 should not be loaded. Pin 9 is the specified output of

the filter; it can typically source/sink 1mA. Driving coaxial

cables or resistive loads less than 20k will degrade the

total harmonic distortion of the filter. When evaluating the

device’s distortion an output buffer is required. A

noninverting buffer, Figure 4, can be used provided that its

input common-mode range is well within the filter’s output

swing.

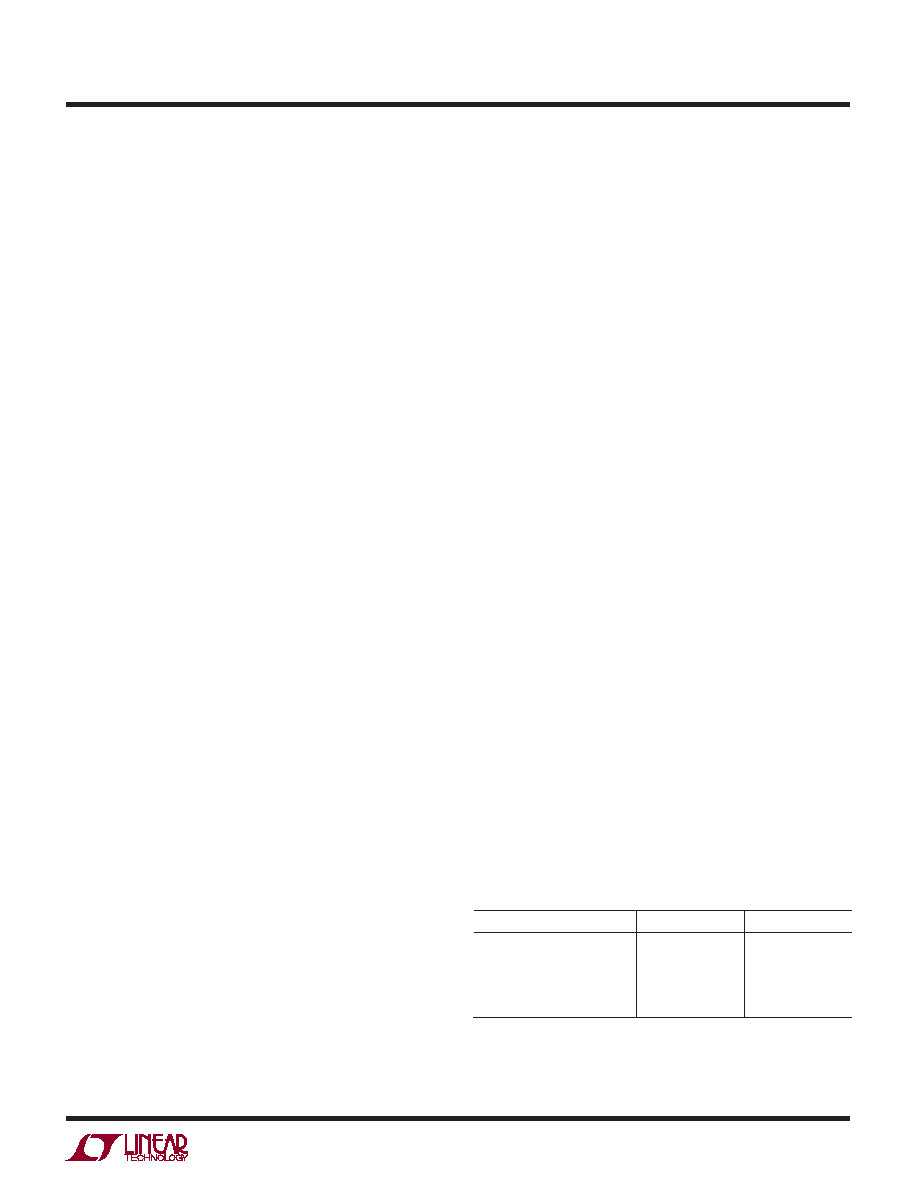

Table 7. Clock Source High and Low Threshold Levels

POWER SUPPLY

HIGH LEVEL

LOW LEVEL

Dual Supply =

±7.5V

≥ 2.18V

≤ 0.5V

Dual Supply =

±5V

≥ 1.45V

≤ 0.5V

Dual Supply =

±2.5V

≥ 0.73V

≤ – 2.0V

Single Supply = 12V

≥ 7.80V

≤ 6.5V

Single Supply = 5V

≥ 1.45V

≤ 0.5V

相关PDF资料 |

PDF描述 |

|---|---|

| LTC1164-6CSW#PBF | IC FILTR 8TH ORDR LOWPASS 16SOIC |

| LTC1164-6CSW | IC FILTR 8TH ORDR LOWPASS 16SOIC |

| MC9S08QB8CWL | MCU 8KB FLASH ULT LP 28SOIC |

| LTC1164-5CSW | IC FILTR 8TH ORDR LOWPASS 16SOIC |

| LTC1064-1CN | IC FILTR 8TH ORDR LOWPASS 14-DIP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC1164-7CSW#PBF | 功能描述:IC FILTR 8TH ORDR LOWPASS 16SOIC RoHS:是 类别:集成电路 (IC) >> 接口 - 滤波器 - 有源 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1,000 系列:- 滤波器类型:连续时间,带通低通 频率 - 截止或中心:150kHz 滤波器数:4 滤波器阶数:8th 电源电压:4.74 V ~ 11 V,±2.37 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) |

| LTC1164-7CSW#TR | 功能描述:IC FILTER LP 8TH ORDER 16SOIC RoHS:否 类别:集成电路 (IC) >> 接口 - 滤波器 - 有源 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1,000 系列:- 滤波器类型:连续时间,带通低通 频率 - 截止或中心:150kHz 滤波器数:4 滤波器阶数:8th 电源电压:4.74 V ~ 11 V,±2.37 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) |

| LTC1164-7CSW#TRPBF | 功能描述:IC FILTR 8TH ORDR LOWPASS 16SOIC RoHS:是 类别:集成电路 (IC) >> 接口 - 滤波器 - 有源 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1,000 系列:- 滤波器类型:连续时间,带通低通 频率 - 截止或中心:150kHz 滤波器数:4 滤波器阶数:8th 电源电压:4.74 V ~ 11 V,±2.37 V ~ 5.5 V 安装类型:表面贴装 封装/外壳:28-SOIC(0.295",7.50mm 宽) 供应商设备封装:28-SOIC W 包装:带卷 (TR) |

| LTC1164-7M | 制造商:LINER 制造商全称:Linear Technology 功能描述:Low Power, Linear Phase 8th Order Lowpass Filter |

| LTC1164-7M/883 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog Filter |

发布紧急采购,3分钟左右您将得到回复。