- 您现在的位置:买卖IC网 > PDF目录19859 > LTC4212IMS#PBF (Linear Technology)IC CTRLR HOTSWAP TIMEOUT 10MSOP PDF资料下载

参数资料

| 型号: | LTC4212IMS#PBF |

| 厂商: | Linear Technology |

| 文件页数: | 11/24页 |

| 文件大小: | 234K |

| 描述: | IC CTRLR HOTSWAP TIMEOUT 10MSOP |

| 标准包装: | 50 |

| 类型: | 热交换控制器 |

| 应用: | 通用 |

| 内部开关: | 无 |

| 电源电压: | 2.5 V ~ 16.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 10-TFSOP,10-MSOP(0.118",3.00mm 宽) |

| 供应商设备封装: | 10-MSOP |

| 包装: | 管件 |

11

LTC4212

4212f

set C

TIMER

= 10nF and adjust its value accordingly to suit

the specific applications.

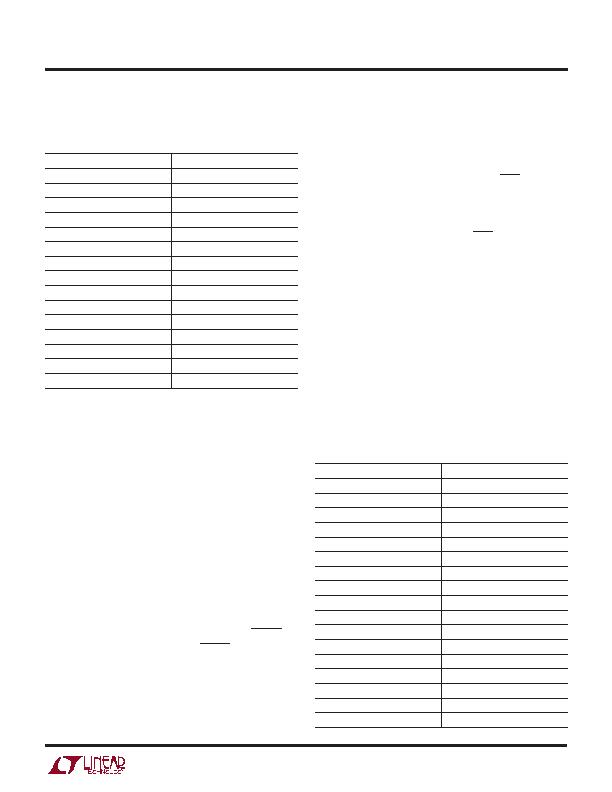

Table 1. t

TIMER

vs C

TIMER

C

TIMER

t

TIMER

0.0033礔

2.0ms

0.0047礔

2.9ms

0.0068礔

4.2ms

0.0082礔

5.1ms

0.01礔

6.2ms

0.015礔

9.3ms

0.022礔

13.6ms

0.033礔

20.4ms

0.047礔

29.0ms

0.068礔

42.0ms

0.082礔

50.7ms

0.1礔

61.8ms

0.15礔

92.7ms

0.22礔

136ms

0.33礔

204ms

Power-Up Timeout Circuit

The power-up timeout circuit has two functions. During

power-up, it trips the circuit breaker if the DC/DC convert-

ers on the board do not power-up and do not enter

regulation on time. After normal power-up, it is configured

to trip the circuit breaker if any of the converters exit

regulation for longer than a programmable delay. Once the

circuit breaker is tripped, the LTC4212 is latched off and

the board is disconnected from the system supply. The ON

pin must be taken low for 120祍 to reset the circuit breaker

and then high to reconnect the board to the backplane

supply.

The power-up timeout circuit uses three pins: PGI or

power good input pin, PGT or power good timer pin and

PGF or power good filter pin. It is enabled at the end of the

second system timing cycle, provided that the FAULT pin

is high. Prior to being enabled or if FAULT is low, the PGT

and PGF pins are pulled to GND by internal N-channel

FETs, M5 and M12 respectively. When enabled, the

power-up timeout circuit starts the power good timer,

which generates a time-out period before the PGI pin is

sampled.

OPERATIO

Power Good Timer

The timer consists of COMP9, M8-M12, two 5礎 current

sources and 0.65V and 0.95V threshold voltages for

COMP9.

The PGI pin is normally connected to the RST output pin

or comparator outputs of an external supply monitor IC or

to the PGOOD pin of a DC/DC converter and drives a

comparator, COMP8 which has a threshold voltage of

1.236V and 28mV of hysterisis. The RST and PGOOD pins

are typically open drain pins and require an external pull-

up resistor. The upper end of the resistor must be con-

nected to a voltage greater than the upper threshold of the

PGI comparator (1.236V).

A capacitor, C

PGT

, connected from the PGT pin to ground

programs the time-out period generated by the power

good timer according to Equation 3. Table 2 shows the

power good time-out periods for a list of standard capaci-

tor values.

t

TIMEOUT

= 1.81& " C

PGT

(3)

Two 5礎 current sources are switched in and out to charge

and discharge C

PGT

between 0.65V and 0.95V for 14

cycles.

Table 2. t

TIMEOUT

vs C

PGT

C

PGT

t

TIMEOUT

3.3nF

5.97ms

4.7nF

8.51ms

6.8nF

12.3ms

8.2nF

14.8ms

0.01礔

18.1ms

0.022礔

39.8ms

0.033礔

59.7ms

0.047礔

85.1ms

0.068礔

123ms

0.082礔

148ms

0.1礔

181ms

0.22礔

136ms

0.33礔

398ms

0.47礔

851ms

0.68礔

1230ms

0.82礔

1480ms

1礔

1810ms

相关PDF资料 |

PDF描述 |

|---|---|

| VE-2W0-CY-F4 | CONVERTER MOD DC/DC 5V 50W |

| FSQ211 | IC FPS PWM/SENSFET 650V 8DIP |

| EMC40DRXI | CONN EDGECARD 80POS DIP .100 SLD |

| MAX8887EZK15+T | IC REG LDO 1.5V .3A TSOT23-5 |

| REC3-0512SR/H1/SMD-R | CONV DC/DC 3W 5VIN 12VOUT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC4213 | 制造商:LINER 制造商全称:Linear Technology 功能描述:No RSENSE? Electronic Circuit Breaker |

| LTC4213CDDB | 制造商:LINER 制造商全称:Linear Technology 功能描述:No RSENSE? Electronic Circuit Breaker |

| LTC4213CDDB#PBF | 制造商:Linear Technology 功能描述:Hot Swap Controller 1-CH 6V 8-Pin DFN EP 制造商:Linear Technology 功能描述:HOT SWAP CNTRL 6V INT SW 8DFN 制造商:Linear Technology 功能描述:HOT SWAP CNTRL, 6V, INT SW, 8DFN |

| LTC4213CDDB#TRMPBF | 功能描述:IC CIRC BREAK ELEC 8-DFN RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

| LTC4213CDDB#TRPBF | 功能描述:IC CIRC BREAK ELEC 8-DFN RoHS:是 类别:集成电路 (IC) >> 专用 IC 系列:* 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:1 系列:- 类型:调帧器 应用:数据传输 安装类型:表面贴装 封装/外壳:400-BBGA 供应商设备封装:400-PBGA(27x27) 包装:散装 |

发布紧急采购,3分钟左右您将得到回复。