- 您现在的位置:买卖IC网 > PDF目录11614 > LTC4310CDD-1#TRPBF (Linear Technology)IC I2C ISOLATOR 100KHZ BUS 10DFN PDF资料下载

参数资料

| 型号: | LTC4310CDD-1#TRPBF |

| 厂商: | Linear Technology |

| 文件页数: | 4/20页 |

| 文件大小: | 0K |

| 描述: | IC I2C ISOLATOR 100KHZ BUS 10DFN |

| 产品培训模块: | LTC4310 - Hot-Swappable I²C Isolators |

| 标准包装: | 2,500 |

| 类型: | 热交换 I²C 隔离器 |

| Tx/Rx类型: | I²C Logic |

| 电容 - 输入: | 10pF |

| 电源电压: | 3 V ~ 5.5 V |

| 电流 - 电源: | 6.5mA |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 10-WFDFN 裸露焊盘 |

| 供应商设备封装: | 10-DFN(3x3) |

| 包装: | 带卷 (TR) |

LTC4310-1/LTC4310-2

12

431012fa

applicaTions inForMaTion

quiet if it has been idle high for at least 115s, or if a STOP

bit has occurred and both data and clock have remained

high since the STOP bit. This functionality makes the

LTC4310 ideal for hot-swapping cards into and out of a

live I2C system. The threshold voltages for the STOP bit

and bus idle comparators are 0.5 VCC.

Stuck Bus Disconnect and Recovery

An internal timer runs whenever SDA, SCL or both are low.

The timer is only reset when both SDA and SCL are high. If

thetimerdoesnotresetwithin37ms,theLTC4310assumes

the bus is stuck low. Accordingly, it ceases driving its SDA

and SCL pins and transmits a special message across the

barrier to inform the other LTC4310. Upon receiving this

message, the other LTC4310 also ceases driving its SDA

and SCL pins. At least 40s after determining the bus

is stuck low, the LTC4310 generates up to sixteen clock

cycles on SCL in an attempt to make the slave release

the SDA line. The LTC4310 stops issuing clocks when the

SDA line releases high, or after sixteen cycles, whichever

comes first. Once the clock pulses have completed, the

LTC4310 issues a STOP bit on SDA and SCL to reset all

devices on the bus.

The LTC4310 reactivates its amplifiers and rise time ac-

celerators when the bus releases high and a STOP bit or

bus idle occurs on both the local and isolated buses, as

previously described in the Start-Up, Data and Clock Hot

Swap Circuitry section. The stuck bus disconnect and re-

covery circuitry is disabled when the LTC4310 is in UVLO,

thermal shutdown and low current shutdown.

Transmit and Receive Circuitry

Transmissions occur on the TXP and TXN pins whenever

the externally driven SDA or SCL logic state changes – in

other words, transmissions are event driven. In addition,

if SDA and SCL do not change state for 1.15ms, the

LTC4310retransmitsthelogicstate.TheTXPandTXNpins

are driven in a pseudo differential fashion. Both pins are

driven to ground when inactive and are driven to 1.25V

(typical)inmatchedsetsofalternating35nspulsestosend

information across the barrier to the other LTC4310.

The LTC4310 receives and decodes the pulses sent by the

other LTC4310 on its RXP and RXN pins. Assuming the

start-up sequence previously described has been com-

pleted, the LTC4310 drives its SDA and SCL lines to the

logic state dictated by the decoded RXP and RXN signals.

The LTC4310 rejects RXP and RXN signals having less

than 500mV magnitude to provide noise immunity against

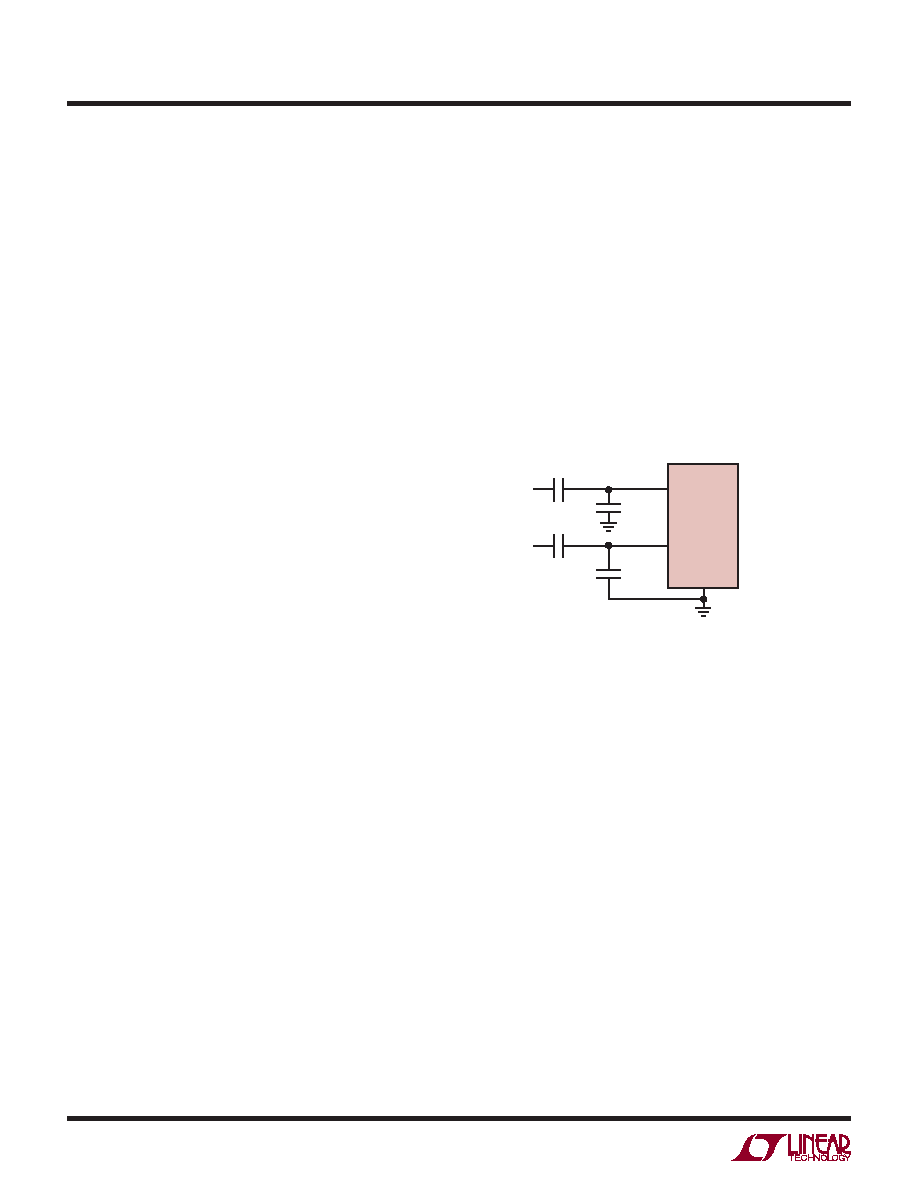

common-modetransients.Theparasiticcapacitancesofthe

LTC4310’s RXP and RXN pins and their associated board

traces form a capacitive divider with the transmit/receive

coupling capacitors, as shown in Figure 6. To guarantee

robustcommunications,minimizetheparasiticcapacitance

CPAR by minimizing the trace length from the coupling

capacitors to the RXP and RXN pins and choose coupling

capacitor values, CRXP and CRXN, that are at least ten

times larger than CPAR.

Figure 6. Parasitic Trace and Pin Capacitances

Form a Capacitive Divider with CRXP and CRXN.

Ensure CRXP , CRXN ≥ 10 CPAR

431012 F06

CRXP

≥47pF

CRXN

≥47pF

GND

RXP

RXN

LTC4310

CPAR1

4.7pF

CPAR2

4.7pF

If the LTC4310 has not received a message in 4.6ms, it

assumes there is a communication problem and ceases

driving its SDA and SCL pins. It also transmits a special

message to the other LTC4310 to inform it that it is no

longer driving its SDA and SCL bus. Upon receiving this

message,theotherLTC4310alsoceasesdrivingitsSDAand

SCL pins. Once the communication problem is resolved,

both LTC4310’s reactivate their amplifiers and rise time

accelerators after a STOP bit or bus idle has occurred on

both buses, as previously described in the Start-Up, Data

and Clock Hot Swap Circuitry section.

Thermal Shutdown

If the die temperature of the LTC4310 exceeds 150°C, the

LTC4310 enters a thermal shutdown mode. It sets TXP

and TXN to a high impedance state, ceases driving SDA

and SCL, and ignores the signals on RXP and RXN. When

the temperature drops back below 130°C, the LTC4310

goes through the POR sequence previously described.

相关PDF资料 |

PDF描述 |

|---|---|

| LTC4310IDD-1#TRPBF | IC I2C ISOLATOR 100KHZ BUS 10DFN |

| LTC4311CDC#TRPBF | IC ACCELERATOR I2C/SMBUS 6-DFN |

| LTC4311CSC6#TRPBF | IC ACCELERATOR SMBUS DL SC70-6 |

| D38999/24MJ4PN | CONN RCPT 56POS JAM NUT W/PINS |

| D38999/26JH53SA | CONN PLUG 53POS STRAIGHT W/SCKT |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC4310CDD-2#PBF | 功能描述:IC I2C ISOLATOR SMBUS 10DFN RoHS:是 类别:集成电路 (IC) >> 接口 - 信号缓冲器,中继器,分配器 系列:- 标准包装:160 系列:- 类型:转发器 Tx/Rx类型:以太网 延迟时间:- 电容 - 输入:- 电源电压:2.37 V ~ 2.63 V 电流 - 电源:60mA 安装类型:表面贴装 封装/外壳:64-TQFP 裸露焊盘 供应商设备封装:64-TQFP-EP(10x10) 包装:托盘 其它名称:Q5134101 |

| LTC4310CDD-2#TRPBF | 功能描述:IC I2C ISOLATOR 400KHZ BUS 10DFN RoHS:是 类别:集成电路 (IC) >> 接口 - 信号缓冲器,中继器,分配器 系列:- 标准包装:160 系列:- 类型:转发器 Tx/Rx类型:以太网 延迟时间:- 电容 - 输入:- 电源电压:2.37 V ~ 2.63 V 电流 - 电源:60mA 安装类型:表面贴装 封装/外壳:64-TQFP 裸露焊盘 供应商设备封装:64-TQFP-EP(10x10) 包装:托盘 其它名称:Q5134101 |

| LTC4310CMS-1#PBF | 功能描述:IC I2C ISOLATOR SMBUS 10MSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 信号缓冲器,中继器,分配器 系列:- 标准包装:160 系列:- 类型:转发器 Tx/Rx类型:以太网 延迟时间:- 电容 - 输入:- 电源电压:2.37 V ~ 2.63 V 电流 - 电源:60mA 安装类型:表面贴装 封装/外壳:64-TQFP 裸露焊盘 供应商设备封装:64-TQFP-EP(10x10) 包装:托盘 其它名称:Q5134101 |

| LTC4310CMS-1#TRPBF | 功能描述:IC I2C ISOLATR 100KHZ BUS 10MSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 信号缓冲器,中继器,分配器 系列:- 标准包装:160 系列:- 类型:转发器 Tx/Rx类型:以太网 延迟时间:- 电容 - 输入:- 电源电压:2.37 V ~ 2.63 V 电流 - 电源:60mA 安装类型:表面贴装 封装/外壳:64-TQFP 裸露焊盘 供应商设备封装:64-TQFP-EP(10x10) 包装:托盘 其它名称:Q5134101 |

| LTC4310CMS-2#PBF | 功能描述:IC I2C ISOLATOR SMBUS 10MSOP RoHS:是 类别:集成电路 (IC) >> 接口 - 信号缓冲器,中继器,分配器 系列:- 标准包装:160 系列:- 类型:转发器 Tx/Rx类型:以太网 延迟时间:- 电容 - 输入:- 电源电压:2.37 V ~ 2.63 V 电流 - 电源:60mA 安装类型:表面贴装 封装/外壳:64-TQFP 裸露焊盘 供应商设备封装:64-TQFP-EP(10x10) 包装:托盘 其它名称:Q5134101 |

发布紧急采购,3分钟左右您将得到回复。