- 您现在的位置:买卖IC网 > PDF目录3492 > LTC6912IDE-1#PBF (Linear Technology)IC PGA DIGITAL R-R DUAL 12-DFN PDF资料下载

参数资料

| 型号: | LTC6912IDE-1#PBF |

| 厂商: | Linear Technology |

| 文件页数: | 10/24页 |

| 文件大小: | 0K |

| 描述: | IC PGA DIGITAL R-R DUAL 12-DFN |

| 标准包装: | 91 |

| 放大器类型: | 可编程增益 |

| 电路数: | 2 |

| 输出类型: | 满摆幅 |

| 转换速率: | 26 V/µs |

| 增益带宽积: | 33MHz |

| 电压 - 输入偏移: | 125µV |

| 电流 - 电源: | 2.25mA |

| 电流 - 输出 / 通道: | 35mA |

| 电压 - 电源,单路/双路(±): | 2.7 V ~ 10.5 V,±2.7 V ~ 5.25 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 12-WFDFN 裸露焊盘 |

| 供应商设备封装: | 12-DFN-EP(4x3) |

| 包装: | 管件 |

LTC6912

18

6912fa

SHDN (GN-16 ONLY): CMOS Compatible Logic Hardware

Shutdown Input. The LTC6912-X has two shutdown modes.

One is a software shutdown state which can be software

programmed into either Channel A, Channel B, or both.

The software shutdown, when programmed to a particular

channel (state = 8), will disable that channel’s amplifier

and tri-state open its analog input and analog output. The

serial interface, however is still active. A hardware shut-

down occurs when the SHDN pin is pulled to the positive

rail. In this condition, both amplifiers and serial interface

are disabled. The SHDN pin is allowed to swing from V– to

10.5V above V–, regardless of V+ so long as the logic levels

meet the minimum requirements specified in the Electrical

Characteristics table. The SHDN pin is a high impedance

CMOS logic input, but has a small pull-down current

source (<10

A) which will force SHDN low if the logic

input is externally floated. On initial power up (with SHDN

open), or coming out of the hardware shutdown mode

(pulling SHDN to V–), both amplifiers are reset into the

power-on reset state (software shutdown mode, state = 8)

for both channels.

CS/LD: TTL/CMOS Compatible Logic Input. When this pin

is asserted low, the CLK pin is enabled, and the 8-bit shift

register serially shifts the shift register contents and

whatever data is present on the DIN pin into the shift

register on the rising edge of CLK. On the rising edge of

CS/LD, the contents of the shift register data are loaded

into the eight bit latch which configures the gain state of

both channel A and channel B amplifiers. A logic high on

CS/LD inhibits the CLK signal internally to the IC.

DIN: TTL/CMOS Compatible Logic Serial Data Input. The

serial interface is synchronously loaded MSB first via DIN

on the rising edge of CLK with CS/LD asserted low.

CLK: TTL/CMOS Compatible Logic Input. With CS/LD

asserted low, the clock synchronizes the loading of the

serial shift register on its rising and falling edges. Data is

shifted in at DIN on the rising edge of CLK and is shifted out

on DOUT on the falling edge of CLK.

DOUT: TTL/CMOS Compatible Logic Output. The MSB of

the shift register contents is shifted out at DOUT on the

falling edge of CLK. The output at DOUT swings between V+

and DGND, and is rated to drive approximately 15pF.

DGND: Digital Ground: The DGND pin defines the potential

from which LOGIC levels VIH and VIL for the 3-wire serial

digital interface are referenced. The recommended con-

nection of DGND depends on how power is applied to the

LTC6912 (See Figures 2, 3, and 4). (CAVEAT: Under no

conditions is DGND to exceed either supply pins V+ and

V–, which could result in damage to the IC if not current

limited.)

Single power supply applications typically use V– for the

system signal ground. The preferred connection for DGND

is therefore V– (See Figure 2).

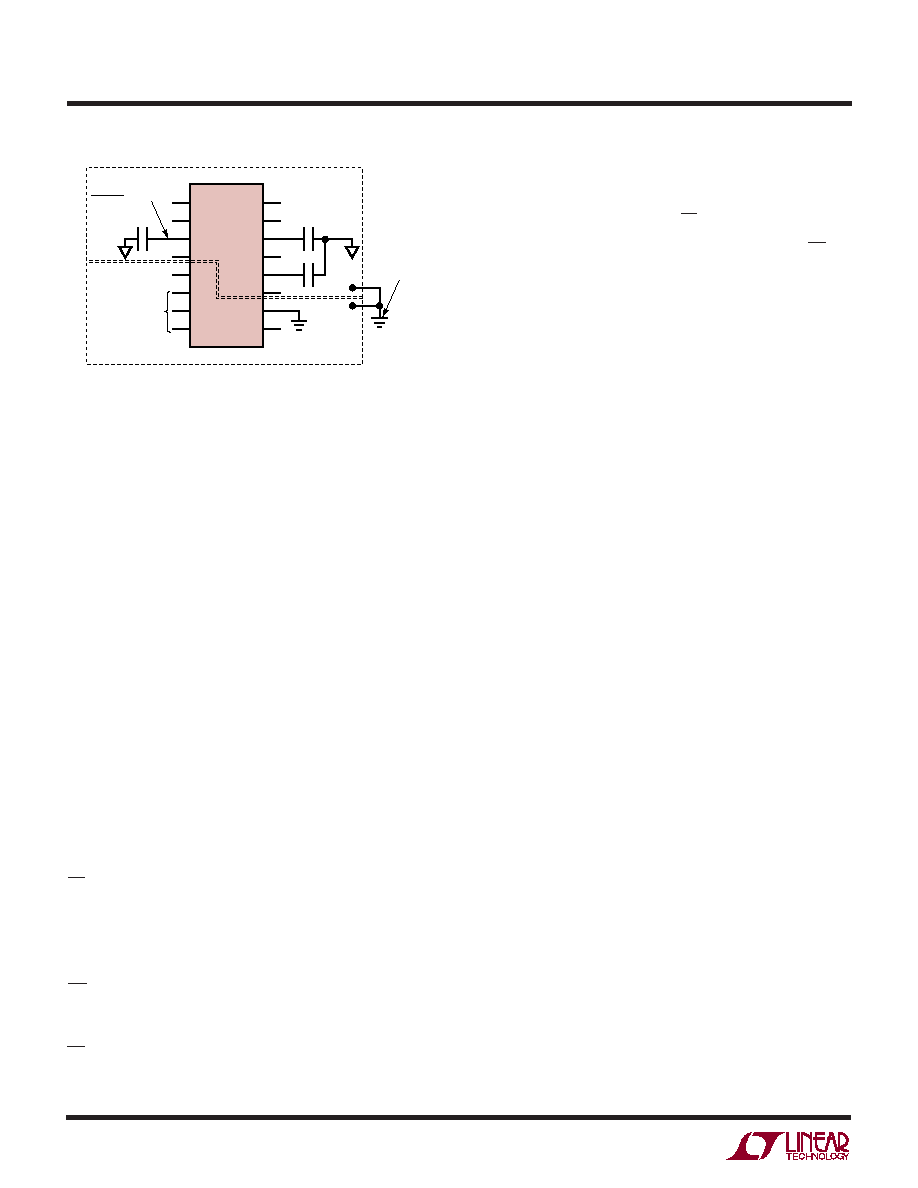

Dual supply applications with symmetrical supplies (such

as

±5V) have a natural system ground potential of zero

volts, in which the DGND pin can be tied to, making the

zero volt ground plane the logic reference (Figure 3).

Finally, if dual asymmetrical power supplies are used, the

system ground is still the natural ground plane voltage.

V–, V+: Power Supply Pins. The V+ and V– pins should be

bypassed with 0.1

F capacitors to an adequate analog

ground plane using the shortest possible wiring. Electri-

cally clean supplies and a low impedance ground are

important for the high dynamic range available from the

LTC6912 (see further details under the AGND pin descrip-

tion). Low noise linear power supplies are recommended.

Switching power supplies require special care to prevent

switching noise coupling into the signal path, reducing

dynamic range.

UU

U

PI FU CTIO S

Figure 4. Asymmetrical Dual Supply Ground Plane Connection

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

LTC6912-X

SERIAL

INTERFACE

0.1

F

0.1

F

V+

V–

DIGITAL GROUND PLANE

ANALOG GROUND PLANE

≥0.1F

V+ + V–

2

REFERENCE

6912 F04

SINGLE-POINT

SYSTEM GND

相关PDF资料 |

PDF描述 |

|---|---|

| CLT-134-02-G-D | CONN RCPT 68POS DUAL 2MM SMD |

| 6-103233-9 | 40 MODII HDR DRST UNSHRD A/PIN |

| 1-87230-6 | 32 MODII HDR DRRA UNSHRD .100 |

| RW3R0DB5R00JET | RES POWER 5.0 OHM 3W 5% SMD |

| FTSH-111-01-L-DV | CONN HEADER 22POS DUAL .05" SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC6912IDE-2 | 制造商:LINER 制造商全称:Linear Technology 功能描述:Dual Programmable Gain Amplifiers with Serial Digital Interface |

| LTC6912IDE-2#PBF | 功能描述:IC PGA DIGITAL R-R DUAL 12-DFN RoHS:是 类别:集成电路 (IC) >> Linear - Amplifiers - Instrumentation 系列:- 标准包装:100 系列:- 放大器类型:通用 电路数:1 输出类型:- 转换速率:0.2 V/µs 增益带宽积:- -3db带宽:- 电流 - 输入偏压:100pA 电压 - 输入偏移:30µV 电流 - 电源:380µA 电流 - 输出 / 通道:- 电压 - 电源,单路/双路(±):±2 V ~ 18 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SO 包装:管件 |

| LTC6912IDE-2#TRPBF | 功能描述:IC PGA DIGITAL R-R DUAL 12-DFN RoHS:是 类别:集成电路 (IC) >> Linear - Amplifiers - Instrumentation 系列:- 标准包装:2,500 系列:- 放大器类型:通用 电路数:2 输出类型:满摆幅 转换速率:350 V/µs 增益带宽积:180MHz -3db带宽:320MHz 电流 - 输入偏压:12.5µA 电压 - 输入偏移:800µV 电流 - 电源:15mA 电流 - 输出 / 通道:85mA 电压 - 电源,单路/双路(±):2.5 V ~ 12.6 V,±1.25 V ~ 6.3 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-TSSOP,8-MSOP(0.118",3.00mm 宽) 供应商设备封装:8-MSOP 包装:带卷 (TR) |

| LTC6912IGN-1 | 制造商:LINER 制造商全称:Linear Technology 功能描述:Dual Programmable Gain Amplifiers with Serial Digital Interface |

| LTC6912IGN-1#PBF | 功能描述:IC PGA DIGITAL R-R DUAL 16SSOP RoHS:是 类别:集成电路 (IC) >> Linear - Amplifiers - Instrumentation 系列:- 标准包装:100 系列:- 放大器类型:通用 电路数:1 输出类型:- 转换速率:0.2 V/µs 增益带宽积:- -3db带宽:- 电流 - 输入偏压:100pA 电压 - 输入偏移:30µV 电流 - 电源:380µA 电流 - 输出 / 通道:- 电压 - 电源,单路/双路(±):±2 V ~ 18 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:8-SOIC(0.154",3.90mm 宽) 供应商设备封装:8-SO 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。