- 您现在的位置:买卖IC网 > PDF目录224116 > M-8888-01 (Clare, Inc.) DTMF Transceiver PDF资料下载

参数资料

| 型号: | M-8888-01 |

| 厂商: | Clare, Inc. |

| 英文描述: | DTMF Transceiver |

| 中文描述: | 双音多频收发器 |

| 文件页数: | 7/14页 |

| 文件大小: | 451K |

| 代理商: | M-8888-01 |

www.clare.com

2

M-8888

Rev. 1

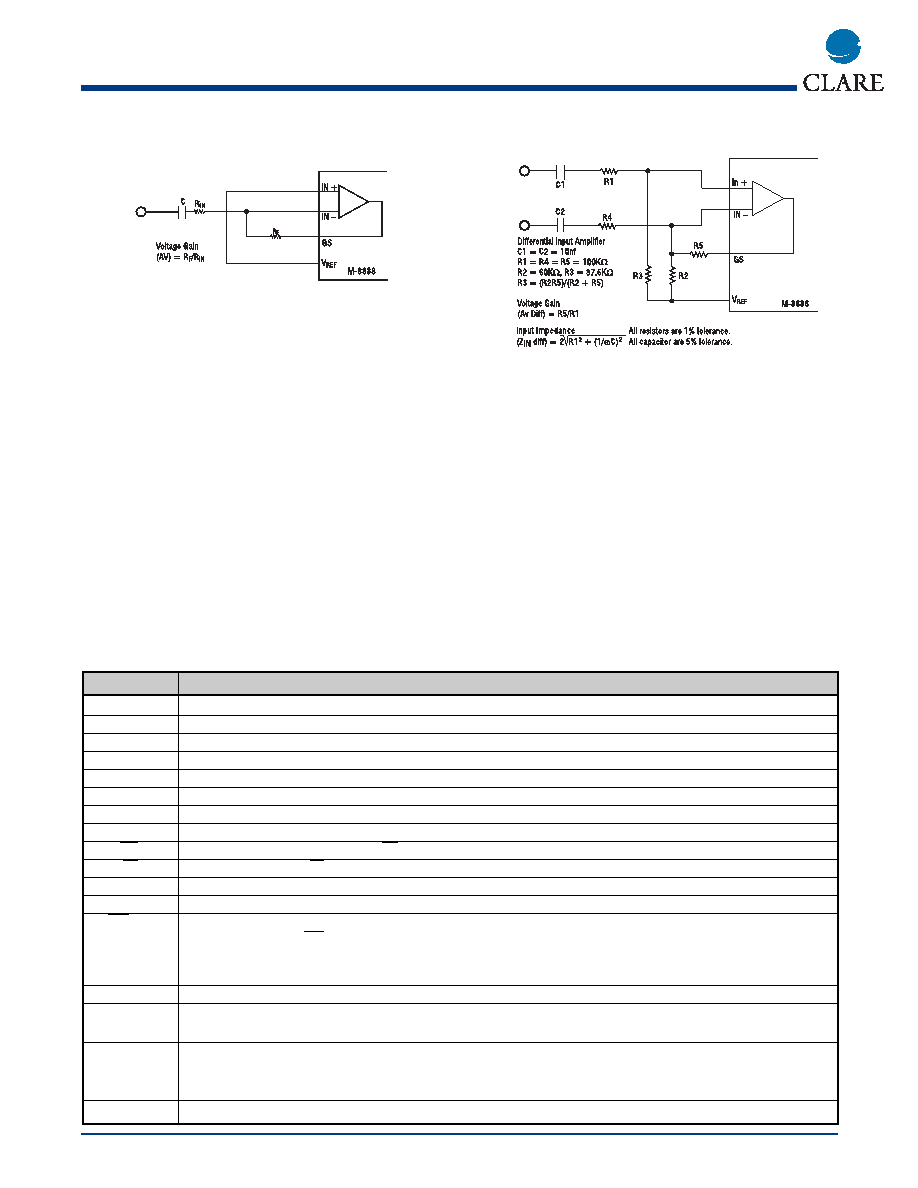

ing the amplifier inputs at V

DD/2. Provisions are made

for the connection of a feedback resistor to the op-amp

output (GS) for gain adjustment. In a single-ended

configuration, the input pins should be connected as

shown in the Single-Ended Input Configuration above.

Differential Input Configuration above shows the nec-

essary connections for a differential input configura-

tion.

Receiver Section

The low and high group tones are separated by apply-

ing the DTMF signal to the inputs of two sixth-order

Single-Ended Input Configuration

Differential Input Configuration

Functional Description

M-8888 functions consist of a high-performance

DTMF receiver with an internal gain setting amplifier

and a DTMF generator that contains a tone burst

counter for generating precise tone bursts and paus-

es. The call progress mode, when selected, allows the

detection of call progress tones. A standard 8051,

8086/8 series microprocessor interface allows access

to an internal status register, two control registers, and

two data registers.

Input Configuration

The input arrangement consists of a differential input

operational amplifier and bias sources (V

REF) for bias-

Pin Functions

Name

Description

IN+

Noninverting op-amp input.

IN-

Inverting op-amp input.

GS

Gain select. Gives access to output of front end differential amplifier for connection of feedback resistor.

V

REF

Reference voltage output. Nominally V

DD/2 is used to bias inputs at mid-rail.

V

SS

Negative power supply input.

OSC1

DTMF clock/oscillator input.

OSC2

Clock output. A 3.5795 MHz crystal connected between OSC1 and OSC2 completes the internal oscillator circuit.

TONE

Dual tone multifrequency (DTMF) output.

WR

Write input. A low on this pin when CS is low enables data transfer from the microprocessor. TTL compatible.

CS

Chip select. TTL input (CS = 0 to select the chip).

RS0

Register select input. See Internal Register Functions on page 7. TTL compatible.

RD

Read input. A low on this pin when CS is low enables data transfer to the microprocessor. TTL compatible..

IRQ /CP

Interrupt request to microprocessor (open-drain output). Also, when call progress (CP) mode has been selected and

interrupt enabled, the IRQ/CP pin will output a rectangular wave signal representative of the input signal applied at the

input op-amp. The input signal must be within the bandwidth limits of the call progress filter. See Timing Diagrams on

page 11.

D0-D3

Microprocessor data bus. TTL compatible.

ESt

Early steering output. Presents a logic high once the digital algorithm has detected a valid tone pair (signal condition).

Any momentary loss of signal condition will cause ESt to return to a logic low.

St/GT

Steering input/guard time output (bidirectional). A voltage greater than V

TSt detected at St causes the device to register

the detected tone pair and update the output latch. A voltage less than V

TSt frees the device to accept a new tone pair. The

GT output acts to reset the external steering time-constant; its state is a function of ESt and the voltage on St.

V

DD

Positive power supply input.

相关PDF资料 |

PDF描述 |

|---|---|

| M-88L70-01P | 3V DTMF Receiver |

| M-88L70-01S | 3V DTMF Receiver |

| M-88L70-01T | 3V DTMF Receiver |

| M-88L70 | 3V DTMF Receiver |

| M-982-02T | Precise Call Progress Tone Detector |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M-8888-01P | 功能描述:IC TRANSCEIVER DTMF CMOS 20-DIP RoHS:是 类别:集成电路 (IC) >> 接口 - 电信 系列:- 产品培训模块:Lead (SnPb) Finish for COTS 产品变化通告:Product Discontinuation 06/Feb/2012 标准包装:750 系列:* |

| M888801SM | 制造商:TELTONE 功能描述: |

| M-8888-01SM | 功能描述:IC TRANSCEIVER DTMF CMOS 20-SOIC RoHS:是 类别:集成电路 (IC) >> 接口 - 电信 系列:- 产品培训模块:Lead (SnPb) Finish for COTS 产品变化通告:Product Discontinuation 06/Feb/2012 标准包装:750 系列:* |

| M-8888-01T | 功能描述:IC TRANSCEIVER DTMF CMOS 20-SOIC RoHS:是 类别:集成电路 (IC) >> 接口 - 电信 系列:- 产品培训模块:Lead (SnPb) Finish for COTS 产品变化通告:Product Discontinuation 06/Feb/2012 标准包装:750 系列:* |

| M888-BDEB | 制造商:SECO 功能描述:QUADMO747-GSERIES W/ CPU T40N 1.0GHZ D. C. @9W, DDR3 2GB, SS - Boxed Product (Development Kits) |

发布紧急采购,3分钟左右您将得到回复。