- 您现在的位置:买卖IC网 > PDF目录180063 > M1A3P400-FPQG208 FPGA, 9216 CLBS, 400000 GATES, 350 MHz, PQFP208 PDF资料下载

参数资料

| 型号: | M1A3P400-FPQG208 |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 9216 CLBS, 400000 GATES, 350 MHz, PQFP208 |

| 封装: | 28 X 28 MM, 3.40 MM HEIGHT, 0.50 MM PITCH, GREEN, PLASTIC, QFP-208 |

| 文件页数: | 29/49页 |

| 文件大小: | 5893K |

| 代理商: | M1A3P400-FPQG208 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页

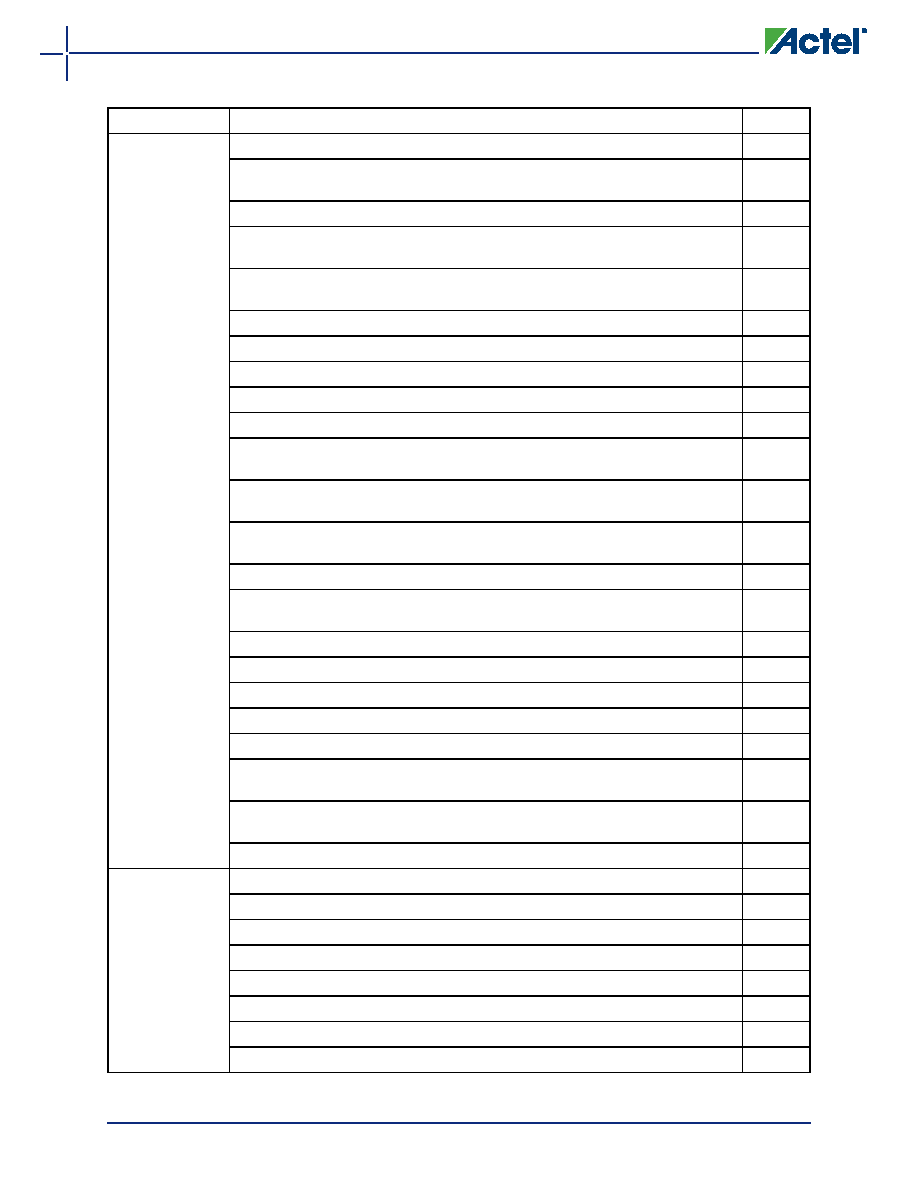

ProASIC3 DC and Switching Characteristics

2- 108

v1.3

Advance v0.3

M7 device information is new.

N/A

Table 2-4 ProASIC3 Globals/Spines/Rows by Device was updated to include the

number or rows in each top or bottom spine.

2-16

EXTFB was removed from Figure 2-24 ProASIC3E CCC Options.

2-24

The "PLL Macro" section was updated. EXTFB information was removed from

this section.

2-15

The CCC Output Peak-to-Peak Period Jitter FCCC_OUT was updated in Table 2-

11 ProASIC3 CCC/PLL Specification

2-29

EXTFB was removed from Figure 2-27 CCC/PLL Macro.

2-28

Table 2-13 ProASIC3 I/O Features was updated.

2-30

The "Hot-Swap Support" section was updated.

2-33

The "Cold-Sparing Support" section was updated.

2-34

"Electrostatic Discharge (ESD) Protection" section was updated.

2-35

The LVPECL specification in Table 2-43 I/O Hot-Swap and 5 V Input Tolerance

Capabilities in ProASIC3 Devices was updated.

2-64

In the Bank 1 area of Figure 2-72, VMV2 was changed to VMV1 and VCCIB2 was

changed to VCCIB1.

2-97

The VJTAG and I/O pin descriptions were updated in the "Pin Descriptions"

section.

2-50

The "JTAG Pins" section was updated.

2-51

"128-Bit AES Decryption" section was updated to include M7 device

information.

2-53

Table 3-6 was updated.

3-6

Table 3-7 was updated.

3-6

In Table 3-11, PAC4 was updated.

3-93-8

Table 3-20 was updated.

3-20

The note in Table 3-32 was updated.

3-27

All Timing Characteristics tables were updated from LVTTL to Register Delays

3-31 to

3-73

The Timing Characteristics for RAM4K9, RAM512X18, and FIFO were updated.

3-85 to

3-90

FTCKMAX was updated in Table 3-110.

3-97

Advance v0.2

Figure 2-11 was updated.

2-9

The "Clock Resources (VersaNets)" section was updated.

2-9

The "VersaNet Global Networks and Spine Access" section was updated.

2-9

The "PLL Macro" section was updated.

2-15

Figure 2-27 was updated.

2-28

Figure 2-20 was updated.

2-19

Table 2-5 was updated.

2-25

Table 2-6 was updated.

2-25

Previous Version

Changes in Current Version (v1.3)

Page

相关PDF资料 |

PDF描述 |

|---|---|

| M1A3P400-1FG144II | FPGA, 9216 CLBS, 400000 GATES, 350 MHz, PBGA144 |

| M1A3P400-1FG256II | FPGA, 9216 CLBS, 400000 GATES, 350 MHz, PBGA256 |

| M1A3P400-1FG484II | FPGA, 9216 CLBS, 400000 GATES, 350 MHz, PBGA484 |

| M1A3P400-1FGG144II | FPGA, 9216 CLBS, 400000 GATES, 350 MHz, PBGA144 |

| M1A3P400-1FGG256II | FPGA, 9216 CLBS, 400000 GATES, 350 MHz, PBGA256 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M1A3P400-FVQ144 | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| M1A3P400-FVQ144ES | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| M1A3P400-FVQ144I | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| M1A3P400-FVQ144PP | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| M1A3P400-FVQG144 | 制造商:ACTEL 制造商全称:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

发布紧急采购,3分钟左右您将得到回复。