- 您现在的位置:买卖IC网 > PDF目录296342 > M2050-11I625.0000 (INTEGRATED DEVICE TECHNOLOGY INC) VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 625 MHz PDF资料下载

参数资料

| 型号: | M2050-11I625.0000 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | XO, clock |

| 英文描述: | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 625 MHz |

| 封装: | LEADLESS, CERAMIC PACKAGE-36 |

| 文件页数: | 5/12页 |

| 文件大小: | 504K |

| 代理商: | M2050-11I625.0000 |

M2050/51/52 Datasheet Rev 1.0

2 of 12

Revised 23Jun2005

Integrate d Circu it Systems, Inc. ● Communications Modules ● www.ics t.com ● tel (508) 852-5400

M2050/51/52

SAW PLL FOR 10GBE 64B/66B FEC

Preliminar y In f o r m atio n

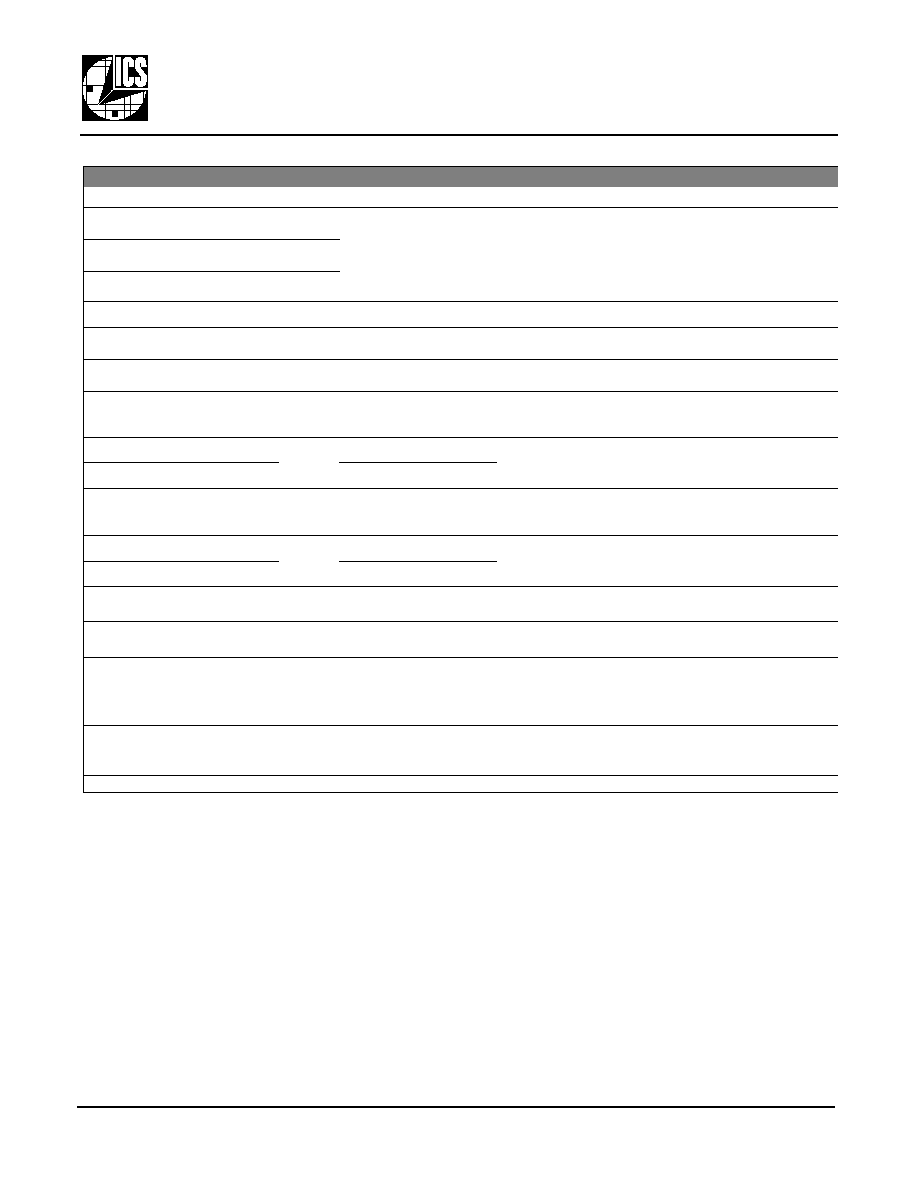

PIN DESCRIPTIONS

Number

Name

I/O

Configuration

Description

1, 2, 3, 10, 14, 26

GND

Ground

Power supply ground connections.

4

9

OP_IN

nOP_IN

Input

External loop filter connections.

5

8

nOP_OUT

OP_OUT

Output

6

7

nVC

VC

Input

11, 19, 33

VCC

Power

Power supply connection, connect to +3.3V.

12

13

FOUT1

nFOUT1

Output

No internal terminator

Clock output pair 1. Differential LVPECL.

15

16

FOUT0

nFOUT0

Output

No internal terminator

Clock output pair 0. Differential LVPECL.

17

18

25

P_SEL1

P_SEL0

P_SEL2

Input

Internal pull-down resistor1

Note 1: For typical values of internal pull-down and pull-up resistors, see DC Characteristics on pg. 10.

Post-PLL , P divider selection. LVCMOS/LVTTL. See Table 7,

20

nDIF_REF1

Input

Biased to Vcc/2 2

Note 2: Biased toVcc/2, with 50k

Reference clock input pair 1. Differential LVPECL or LVDS.

Resistor bias on inverting terminal supports TTL or LVCMOS.

21

DIF_REF1

Internal pull-down resistor1

22

REF_SEL

Input

Internal pull-down resistor1

Reference clock input selection. LVCMOS/LVTTL:

Logic 1 selects DIF_REF1, nDIF_REF1.

Logic 0 selects DIF_REF0, nDIF_REF0.

23

nDIF_REF0

Input

Biased to Vcc/2 2

Reference clock input pair 0. Differential LVPECL or LVDS.

Resistor bias on inverting terminal supports TTL or LVCMOS.

24

DIF_REF0

Internal pull-down resistor 1

27

28

FIN_SEL1

FIN_SEL0

Input

Internal pull-down resistor1

I

nput clock frequency selection. LVCMOS/LVTTL. See

29

30

FEC_SEL0

FEC_SEL1

Input

Internal pull-down resistor1

Mfec and Rfec divider value selection. LVCMOS/ LVTTL.

31

LOL

Output

Loss of Lock indicator output. Asserted when internal PLL is

not tracking the input reference for frequency and phase. 3

Logic 1 indicates loss of lock.

Logic 0 indicates locked condition.

32

NBW

Input

Internal pull-UP resistor1

Narrow Bandwidth enable. LVCMOS/LVTTL:

Logic 1 - Narrow loop bandwidth, R

IN = 2100k.

Logic 0 - Wide bandwidth, R

IN = 100k.

34, 35, 36

DNC

Do Not Connect.

Table 2: Pin Descriptions

相关PDF资料 |

PDF描述 |

|---|---|

| M2050-12I690.5692 | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 690.5692 MHz |

| M2051-12-690.5692 | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 690.5692 MHz |

| M2051-12IFREQ | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 15 MHz - 700 MHz |

| M2052-11-625.0000 | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 625 MHz |

| M2050-11I622.0800 | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 622.08 MHz |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M2050-11I644.5313 | 制造商:ICS 制造商全称:ICS 功能描述:SAW PLL FOR 10GBE 64B/66B FEC |

| M2050-11I693.4830 | 制造商:Integrated Device Technology Inc 功能描述:FREQUENCY TRANSLATOR 制造商:Integrated Device Technology Inc 功能描述:9X9 LCC(LEAD FREE) - Bulk |

| M2050-11I693.4830T | 制造商:Integrated Device Technology Inc 功能描述:FREQUENCY TRANSLATOR 制造商:Integrated Device Technology Inc 功能描述:9X9 LCC(LEAD FREE) - Tape and Reel |

| M2050HCZ10 | 制造商:n/a 功能描述:Ships in 2 days |

| M2051 | 制造商:ICS 制造商全称:ICS 功能描述:SAW PLL FOR 10GBE 64B/66B FEC |

发布紧急采购,3分钟左右您将得到回复。