- 您现在的位置:买卖IC网 > PDF目录296342 > M2050-11I690.5692 (INTEGRATED DEVICE TECHNOLOGY INC) VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 690.5692 MHz PDF资料下载

参数资料

| 型号: | M2050-11I690.5692 |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | XO, clock |

| 英文描述: | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 690.5692 MHz |

| 封装: | LEADLESS, CERAMIC PACKAGE-36 |

| 文件页数: | 7/12页 |

| 文件大小: | 504K |

| 代理商: | M2050-11I690.5692 |

M2050/51/52 Datasheet Rev 1.0

4 of 12

Revised 23Jun2005

Integrate d Circu it Systems, Inc. ● Communications Modules ● www.ics t.com ● tel (508) 852-5400

M2050/51/52

SAW PLL FOR 10GBE 64B/66B FEC

Preliminar y In f o r m atio n

M2051: De-map LUT (10GbE LAN or 255/238 FEC to 10GbE)

Use this option to demap from either “10GbE LAN” or

“10GbE 255/238 FEC” encoded to “10GbE”. Also use

this option to operate in 10GbE repeater mode.

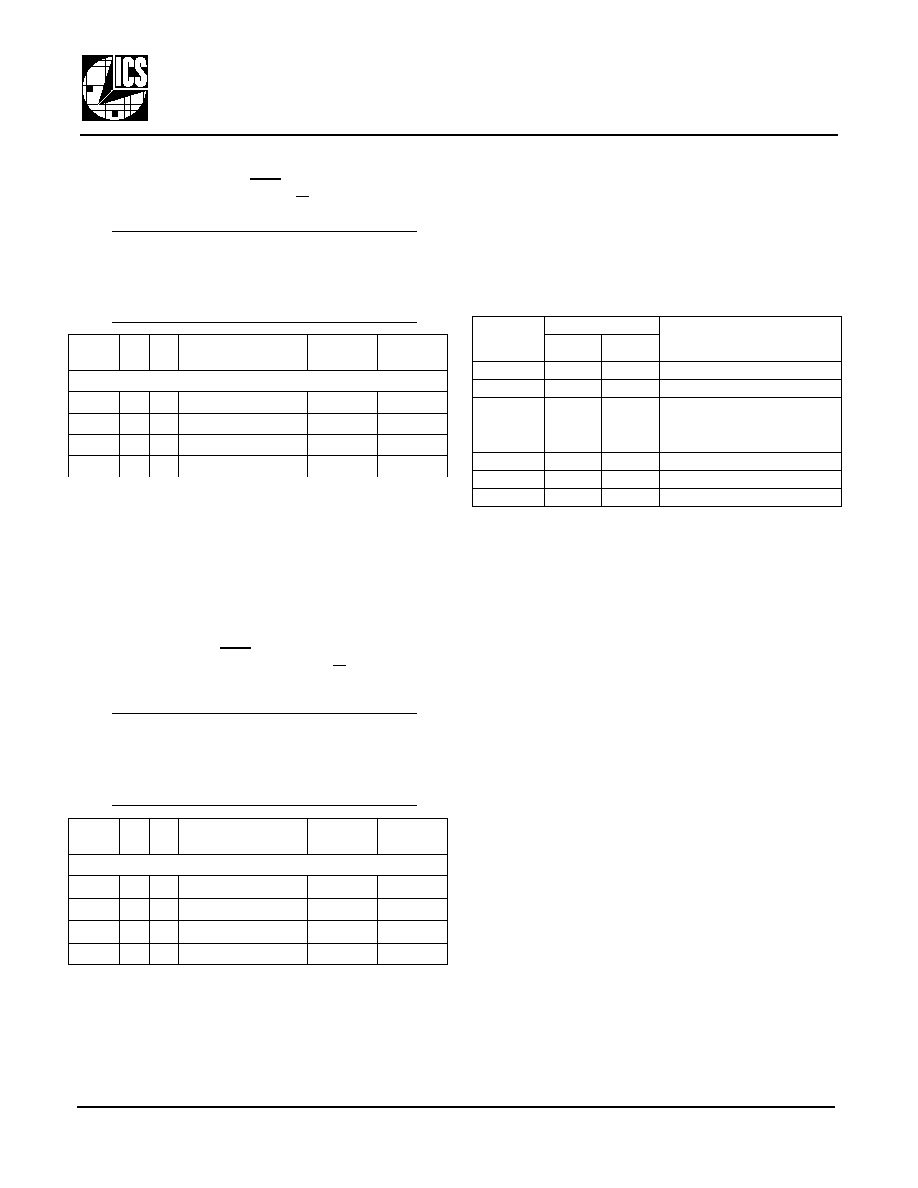

The de-mapper FEC PLL ratios (in Table 5) enables

the M2051-11-625.0000 to accept “base” input

reference frequencies of:

625.00

MHz (“10GbE”),

644.5313

MHz (“10GbE LAN”), and

669.6429

MHz (“10GbE 255/238 FEC”).

The Mfec divider value for the first three settings allows

one set of passive filter components to be used for all

three of these modes.

The fourth setting maps “10GbE 255/238 FEC” using

the lowest Mfec value possible. Use this setting to

produce the maximum loop bandwidth.

M2052: De-map LUT (255/237 or 255/238 FEC to 10GbE LAN)

This option de-maps from both “10GbE LAN 255/237

FEC” and “10GbE LAN 255/238 FEC” to “10GbE LAN”.

Also use this option to operate in 10GbE LAN repeater

mode.

The de-mapper FEC PLL ratios (in Table 6) enables

the M2052-11-625.0000 to accept “base” input

reference frequencies of:

644.5313

MHz (“10GbE LAN”),

690.5692

MHz (“10GbE LAN 255/238 FEC”), and

693.4830

MHz (“10GbE LAN 255/237 FEC”).

Use this option for multi-rate de-mapping applications

that require one set of PLL passive filter values to

operate over both “10GbE LAN 255/237 FEC” and

“10GbE LAN 255/238 FEC”. The Mfec divider value is

kept nearly constant to maintain similar loop bandwidth

using one set of external filter component values.

P Divider Look-Up Table (LUT)

The P_SEL2:0 pins select the P divider values, which set

the output clock frequencies. A P divider of value of 1

will provide a 625.00MHz output when using a 625.00MHz

VCSO, for example. P divider values of 4, 5, or 25 are

also available, plus a TriState mode. The outputs can

be placed into the valid state combinations as listed in

Table 7. (The outputs cannot each be placed into any of

the five available states independently.)

General Guideline for Mfec and Rfec Divider Selection

When LOL is to be used for system health monitoring,

the phase detector frequency should be 5MHz or

greater. Low phase detector frequencies make LOL

overly sensitive, and higher phase detector frequencies

make LOL less sensitive. The LOL pin should not be used

during loop timing mode.

FUNCTIONAL DESCRIPTION

The M2050/51/52 is a PLL (Phase Locked Loop) based

clock generator that generates output clocks synchro-

nized to one of two selectable input reference clocks.

An internal high "Q" SAW delay line provides low jitter

signal performance and establishes the output

frequency of the VCSO (Voltage Controlled SAW

Oscillator). In a given M2050/51/52 device, the VCSO

center frequency is fixed. A common center frequency

is 625.00MHz, for 10GbE 64b/66b optical network

applications. The VCSO center frequency is specified at

time of order (see “Ordering Information” on pg. 12).

The VCSO has a guaranteed tuning range of ±120 ppm

(commercial temperature grade).

Pin selectable dividers are used within the PLL and

for the output clock. This enables tailoring of device

functionality and performance. The FEC feedback and

reference dividers (the “Mfec Divider” and “Rfec

Divider”) provide the multiplication ratios necessary to

accomodate clock translation for both forward and

inverse Forward Error Correction. The Mfec and Rfec

FEC_SEL1:0

1

0

Mfec Rfec

Description

Base Input

Rate (MHz)

Fvcso =

Base Output

Rate (MHz)

For M2051 with Fvcso = 625.00

0 0

32 33 10GbE LAN to 10GbE

644.5313 625.0000

0 1

32 32 10GbE jitter attenuator

625.0000 625.0000

1 0

28 30 10GbE 255/238 FEC to 10GbE 669.6429 625.0000

1 1

14 15 10GbE 255/238 FEC to 10GbE 669.6429 625.0000

FEC_SEL1:0

1

0

Mfec Rfec

Description

Base Input

Rate (MHz)

Fvcso =

Base Output

Rate (MHz)

For M2052 with Fvcso = 625.00

0 0

79 85

10GbE LAN

255/237 FEC to

10GbE LAN

693.4830 625.0000

0 1

79 79 10GbE LAN jitter attenuator

644.5313 625.0000

1 0

84 90

10GbE LAN

255/238 FEC to

10GbE LAN

690.5692 625.0000

1 1

84 84 10GbE LAN jitter attenuator

644.5313 625.0000

P_SEL2:0

P Value

M2050-625.0000

Output Frequency (MHz)

FOUT0

FOUT1

for FOUT0 for FOUT1

0 0 0

25

1

25.00 625.00

0 0 1

25

4

25.00 156.25

0 1 0

1

625.00 625.00

0 1 1

4

1

156.25 625.00

1 0 0

5

125.00 125.00

1 0 1

4

156.25 156.25

1 1 0

5

4

125.00 156.25

1 1 1

TriState TriState

N/A

Table 7: P Divider Look-Up Table (LUT)

相关PDF资料 |

PDF描述 |

|---|---|

| M2050-11IFREQ | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 15 MHz - 700 MHz |

| M2050-12I672.1600 | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 672.16 MHz |

| M2050-13-644.5313 | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 644.5313 MHz |

| M2050-13-669.1281 | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 669.1281 MHz |

| M2050-13-672.1600 | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 672.16 MHz |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M2050-11I693.4830 | 制造商:Integrated Device Technology Inc 功能描述:FREQUENCY TRANSLATOR 制造商:Integrated Device Technology Inc 功能描述:9X9 LCC(LEAD FREE) - Bulk |

| M2050-11I693.4830T | 制造商:Integrated Device Technology Inc 功能描述:FREQUENCY TRANSLATOR 制造商:Integrated Device Technology Inc 功能描述:9X9 LCC(LEAD FREE) - Tape and Reel |

| M2050HCZ10 | 制造商:n/a 功能描述:Ships in 2 days |

| M2051 | 制造商:ICS 制造商全称:ICS 功能描述:SAW PLL FOR 10GBE 64B/66B FEC |

| M2051-11-625.0000 | 制造商:Integrated Device Technology Inc 功能描述:PLL Single 36-Pin CLCC 制造商:Integrated Device Technology Inc 功能描述:FREQUENCY TRANSLATOR |

发布紧急采购,3分钟左右您将得到回复。