- 您现在的位置:买卖IC网 > PDF目录69011 > M34524M8-XXXFP 4-BIT, MROM, 6 MHz, MICROCONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | M34524M8-XXXFP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 4-BIT, MROM, 6 MHz, MICROCONTROLLER, PQFP64 |

| 封装: | 14 X 14 MM, 0.80 MM PITCH, PLASTIC, QFP-64 |

| 文件页数: | 10/66页 |

| 文件大小: | 1936K |

| 代理商: | M34524M8-XXXFP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页

Rev.1.04

Aug 23, 2007

Page 18 of 146

REJ03B0188-0104

4559 Group

FUNCTION BLOCK OPERATIONS

CPU

(1) Arithmetic logic unit (ALU)

The arithmetic logic unit ALU performs 4-bit arithmetic such as

4-bit data addition, comparison, AND operation, OR operation,

and bit manipulation.

(2) Register A and carry flag

Register A is a 4-bit register used for arithmetic, transfer,

exchange, and I/O operation.

Carry flag CY is a 1-bit flag that is set to “1” when there is a

carry with the AMC instruction (Figure 12).

It is unchanged with both A n instruction and AM instruction.

The value of A0 is stored in carry flag CY with the RAR

instruction (Figure 13).

Carry flag CY can be set to “1” with the SC instruction and

cleared to “0” with the RC instruction.

(3) Registers B and E

Register B is a 4-bit register used for temporary storage of 4-bit

data, and for 8-bit data transfer together with register A.

Register E is an 8-bit register. It can be used for 8-bit data

transfer with register B used as the high-order 4 bits and register

A as the low-order 4 bits (Figure 14).

Register E is undefined after system is released from reset and

returned from the power down mode. Accordingly, set the initial

value.

(4) Register D

Register D is a 3-bit register.

It is used to store a 7-bit ROM address together with register A

and is used as a pointer within the specified page when the TABP

p, BLA p, or BMLA p instruction is executed (Figure 15).

Also, when the TABP p instruction is executed at UPTF flag =

“1”, the high-order 2 bits of ROM reference data is stored to the

low-order 2 bits of register D, the high-order 1 bit of register D is

“0”.

When the TABP p instruction is executed at UPTF flag = “0”, the

contents of register D remains unchanged. The UPTF flag is set

to “1” with the SUPT instruction and cleared to “0” with the

RUPT instruction.

The initial value of UPTF flag is “0”.

Register D is undefined after system is released from reset and

returned from the power down mode. Accordingly, set the initial

value.

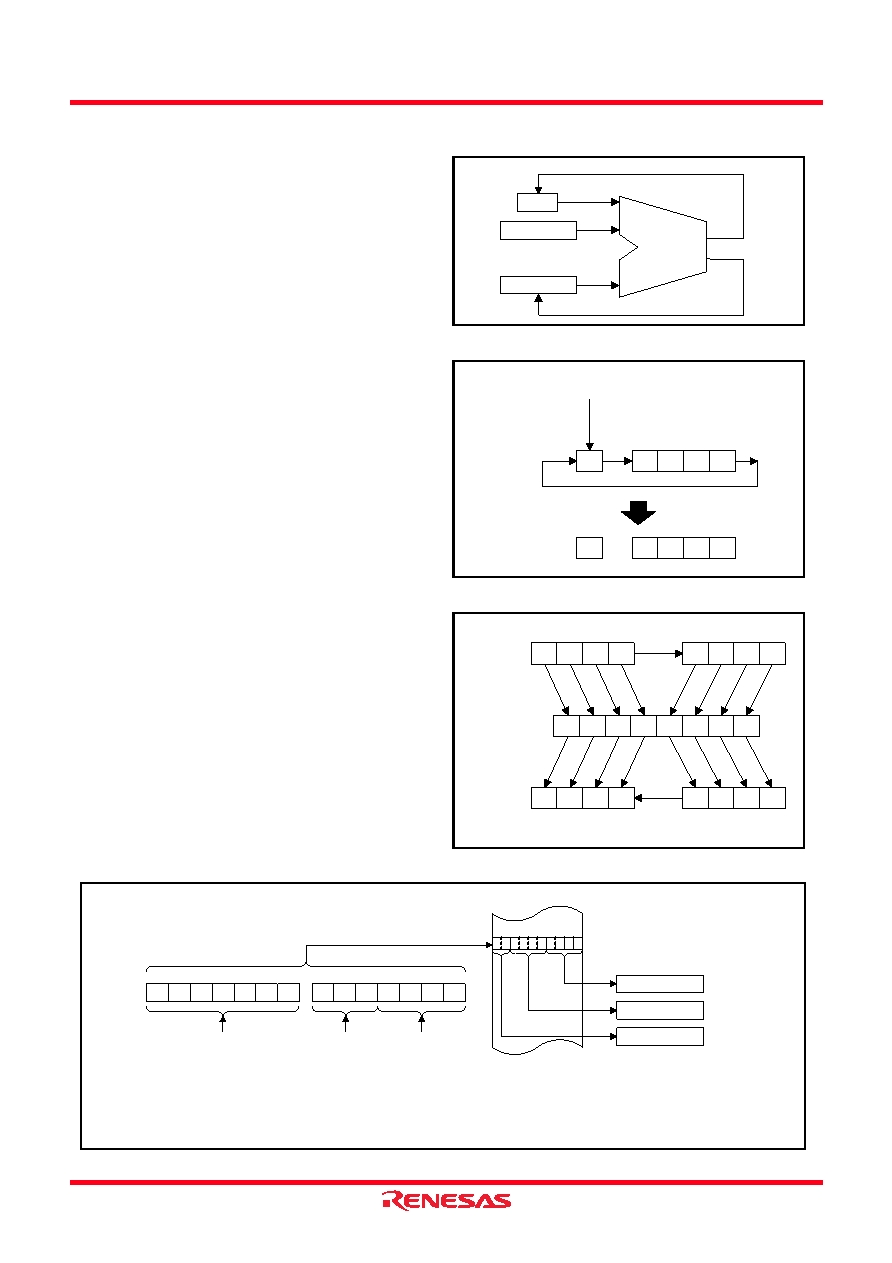

Fig 12. AMC instruction execution example

Fig 13. RAR instruction execution example

Fig 14. Registers A, B and register E

Fig 15. TABP p instruction execution example

(CY)

<Result>

(M(DP))

(A)

Addition

ALU

<Carry>

<Clear>

RC instruction

<Set>

SC instruction

CY

A3 A2 A1 A0

<Rotation>

RAR instruction

A0

CY A3 A2 A1

TABE instruction

TEAB instruction

A3 A2 A1 A0

Register A

TAB instruction

E3 E2 E1 E0

E7 E6 E5 E4

B3 B2 B1 B0

Register B

Register E

A3 A2 A1 A0

Register A

TBA instruction

B3 B2 B1 B0

Register B

A3 A2 A1 A0

DR2 DR1 DR0

PCL

Register A (4)

Low-order 2 bits

Register D (3)

Register B (4)

Middle-order 2 bits

ROM

Field value p

The contents

of register D

Specifying address

TABP p

instruction

p3

p2

p1

p0

p6

p5

p4

PCH

84

0

The contents

of register A

High-order 2 bits

Flag UPTF = 1;

High-order 2 bits of reference data is transferred to the low-order 2

bits of register D.

“0” is stored to the high-order 1 bit of register D.

Flag UPTF = 0;

Data is not transferred to register D.

相关PDF资料 |

PDF描述 |

|---|---|

| M34524EDFP | 4-BIT, OTPROM, 6 MHz, MICROCONTROLLER, PQFP64 |

| M34551E8-XXXFP | 4-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PQFP48 |

| M34551E8FP | 4-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PQFP48 |

| M34551M4-XXXFP | 4-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP48 |

| M34552G8FP | 4-BIT, OTPROM, 6 MHz, MICROCONTROLLER, PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M34524MC-XXXFP | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:4-BIT CISC SINGLE-CHIP MICROCOMPUTER 720 FAMILY / 4500 SERIES |

| M3452-C09K1 | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING TRANSISTOR |

| M3452-C125K2 | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING TRANSISTOR |

| M3452-C125K2,A | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING TRANSISTOR |

| M3452-C150B7 | 制造商:Bonitron 功能描述:OVERVOLTAGE BRAKING TRANSISTOR |

发布紧急采购,3分钟左右您将得到回复。