- 您现在的位置:买卖IC网 > PDF目录383294 > M34D64-R (意法半导体) 64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory PDF资料下载

参数资料

| 型号: | M34D64-R |

| 厂商: | 意法半导体 |

| 元件分类: | DRAM |

| 英文描述: | 64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| 中文描述: | 64千位串行I2C总线的EEPROM,带有硬件写控制记忆的热门季 |

| 文件页数: | 6/21页 |

| 文件大小: | 147K |

| 代理商: | M34D64-R |

M34D64

6/21

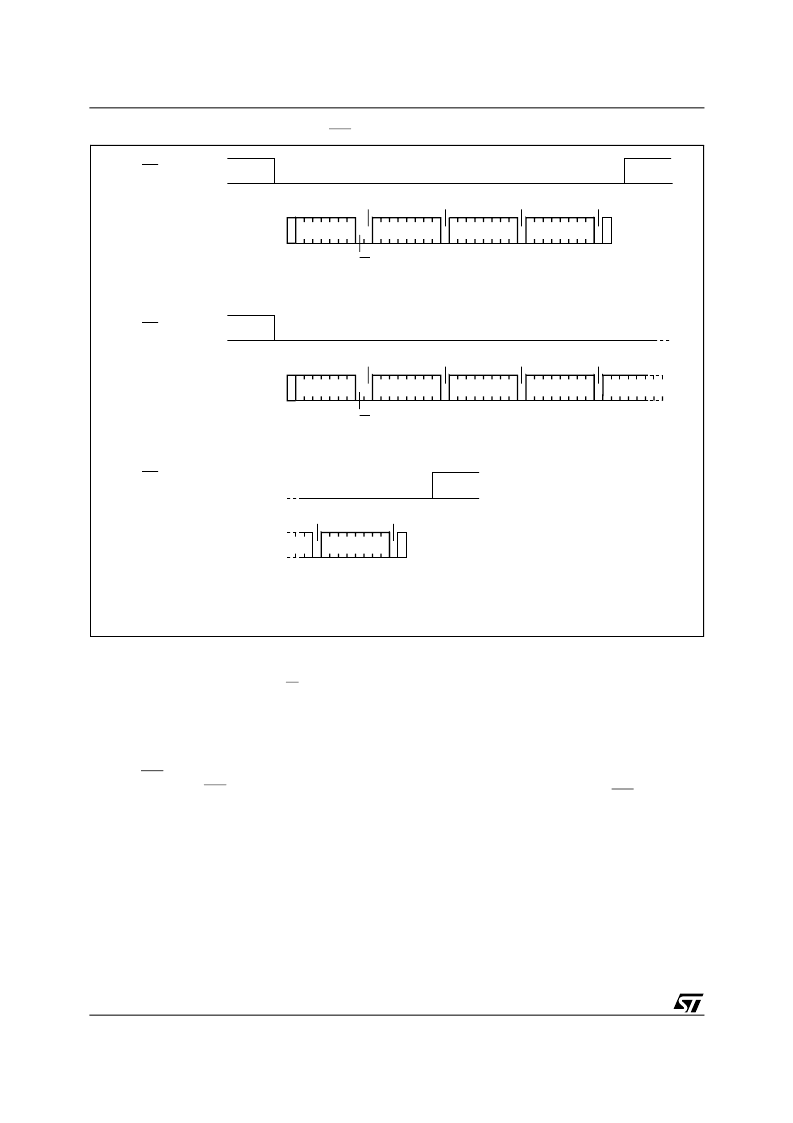

Figure 7. Write Mode Sequences with WC=0 (data write enabled)

Write Operations

Following a Start condition the bus master sends

a Device Select Code with the RW bit reset to 0.

The device acknowledges this, as shown in Figure

7, and waits for two address bytes. The device re-

sponds to each address byte with an acknowledge

bit, and then waits for the data byte(s).

Writing to the memory may be inhibited if Write

Control (WC) is driven High. Any Write instruction

with Write Control (WC) driven High (during a pe-

riod of time from the Start condition until the end of

the two address bytes) will not modify the contents

of the top quarter of the memory.

Each data byte in the memory has a 16-bit (two

byte wide) address. The Most Significant Byte (Ta-

ble 3) is sent first, followed by the Least Significant

Byte (Table 4). Bits b15 to b0 form the address of

the byte in memory.

When the bus master generates a Stop condition

immediately after the Ack bit (in the “10

th

bit” time

slot), either at the end of a Byte Write or a Page

Write, the internal memory Write cycle is triggered.

A Stop condition at any other time slot does not

trigger the internal Write cycle.

During the internal Write cycle, Serial Data (SDA)

is disabled internally, and the device does not re-

spond to any requests.

Byte Write

After the Device Select code and the address

bytes, the bus master sends one data byte. If the

addressed location is Write-protected (top quarter

of the memory), by Write Control (WC) being driv-

en High, the location is not modified. The bus mas-

ter terminates the transfer by generating a Stop

condition, as shown in Figure 7.

Page Write

The Page Write mode allows up to 32 bytes to be

written in a single Write cycle, provided that they

are all located in the same ’row’ in the memory:

that is, the most significant memory address bits

(b12-b5) are the same. If more bytes are sent than

will fit up to the end of the row, a condition known

as ‘roll-over’ occurs. This should be avoided, as

S

S

BYTE WRITE

DEV SEL

BYTE ADDR

BYTE ADDR

DATA IN

WC

S

PAGE WRITE

DEV SEL

BYTE ADDR

BYTE ADDR

DATA IN 1

WC

DATA IN 2

AI01106C

PAGE WRITE

(cont'd)

WC (cont'd)

S

DATA IN N

ACK

R/W

ACK

ACK

ACK

ACK

ACK

ACK

ACK

R/W

ACK

ACK

相关PDF资料 |

PDF描述 |

|---|---|

| M34D64-RDW6T | 64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64-RMN6T | 64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64-W | 64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64-WDW6T | 64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64-WMN6T | 64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M34D64RBNT1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64/32 Kbit Serial IC Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64RBNT5 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64/32 Kbit Serial IC Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64RBNT6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64/32 Kbit Serial IC Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64-RDW6T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64-RMN6T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

发布紧急采购,3分钟左右您将得到回复。