- 您现在的位置:买卖IC网 > PDF目录383294 > M34D64-RDW6T (意法半导体) 64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory PDF资料下载

参数资料

| 型号: | M34D64-RDW6T |

| 厂商: | 意法半导体 |

| 元件分类: | DRAM |

| 英文描述: | 64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| 中文描述: | 64千位串行I2C总线的EEPROM,带有硬件写控制记忆的热门季 |

| 文件页数: | 3/21页 |

| 文件大小: | 147K |

| 代理商: | M34D64-RDW6T |

3/21

M34D64

SIGNAL DESCRIPTION

Serial Clock (SCL)

This input signal is used to strobe all data in and

out of the device. In applications where this signal

is used by slave devices to synchronize the bus to

a slower clock, the bus master must have an open

drain output, and a pull-up resistor must be con-

nected from Serial Clock (SCL) to V

CC

. (Figure 5

indicates how the value of the pull-up resistor can

be calculated). In most applications, though, this

method of synchronization is not employed, and

so the pull-up resistor is not necessary, provided

that the bus master has a push-pull (rather than

open drain) output.

Serial Data (SDA)

This bi-directional signal is used to transfer data in

or out of the device. It is an open drain output that

may be wire-OR’ed with other open drain or open

collector signals on the bus. A pull up resistor must

be connected from Serial Data (SDA) to V

CC

. (Fig-

ure 5 indicates how the value of the pull-up resistor

can be calculated).

Chip Enable (E0, E1, E2)

These input signals are used to set the value that

is to be looked for on the three least significant bits

(b3, b2, b1) of the 7-bit Device Select Code. These

inputs must be tied to V

CC

or V

SS

, to establish the

Device Select Code.

Write Control (WC)

The hardware Write Control pin (WC) is useful for

protecting the top quarter of the memory (as

shown in Figure 4) from inadvertent erase or write.

The Write Control signal is used to enable

(WC=V

IL

) or disable (WC=V

IH

) write instructions to

the top quarter of the memory area. When uncon-

nected, the WC input is internally read as V

IL

, and

write operations are allowed.

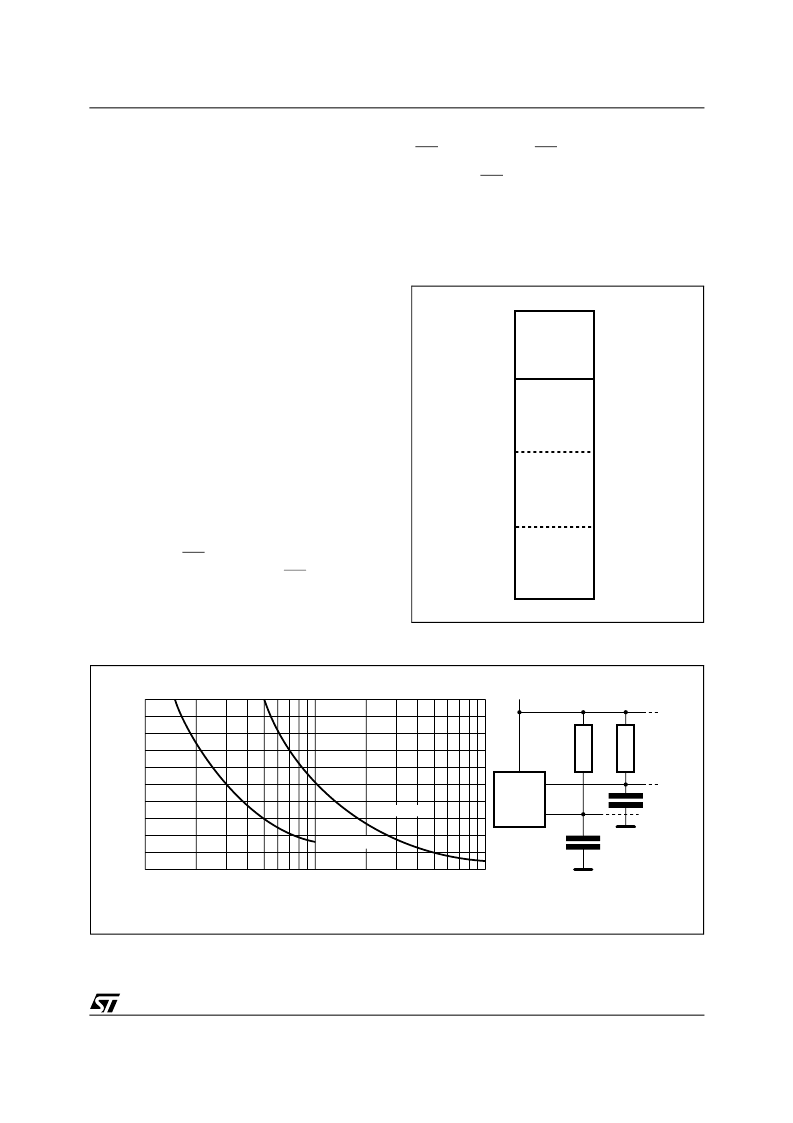

Figure 4. Memory Map showing Write Control

Area

Figure 5. Maximum R

L

Value versus Bus Capacitance (C

BUS

) for an I

2

C Bus

AI03114C

1FFFh

Write Controlled

Area

1000h

0000h

0800h

1800h

AI01665

VCC

CBUS

SDA

RL

MASTER

RL

SCL

CBUS

100

0

4

8

12

16

20

CBUS (pF)

M

)

10

1000

fc = 400kHz

fc = 100kHz

相关PDF资料 |

PDF描述 |

|---|---|

| M34D64-RMN6T | 64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64-W | 64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64-WDW6T | 64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64-WMN6T | 64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M35062-001SP | SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M34D64-RMN6T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64RMNT1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64/32 Kbit Serial IC Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64RMNT5 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64/32 Kbit Serial IC Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64RMNT6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64/32 Kbit Serial IC Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64-W | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit Serial I2C Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

发布紧急采购,3分钟左右您将得到回复。