- 您现在的位置:买卖IC网 > PDF目录296384 > M38223MAXXXGP (Mitsubishi Electric Corporation) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF资料下载

参数资料

| 型号: | M38223MAXXXGP |

| 厂商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 单芯片8位CMOS微机 |

| 文件页数: | 15/78页 |

| 文件大小: | 998K |

| 代理商: | M38223MAXXXGP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页

22

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

3822 Group

MITSUBISHI MICROCOMPUTERS

INTERRUPTS

Interrupts occur by seventeen sources: eight external, eight inter-

nal, and one software.

Interrupt Control

Each interrupt is controlled by an interrupt request bit, an interrupt

enable bit, and the interrupt disable flag except for the software

interrupt set by the BRK instruction. An interrupt occurs if the cor-

responding interrupt request and enable bits are “1” and the

interrupt disable flag is “0”.

Interrupt enable bits can be set or cleared by software.

Interrupt request bits can be cleared by software, but cannot be

set by software.

The BRK instruction cannot be disabled with any flag or bit. The I

flag disables all interrupts except the BRK instruction interrupt.

When several interrupts occur at the same time, the interrupts are

received according to priority.

Interrupt Operation

Upon acceptance of an interrupt the following operations are auto-

matically performed:

1. The contents of the program counter and processor status

register are automatically pushed onto the stack.

2. The interrupt disable flag is set and the corresponding

interrupt request bit is cleared.

3. The interrupt jump destination address is read from the vec-

tor table into the program counter.

sNotes on interrupts

When setting the followings, the interrupt request bit may be set to

“1”.

When setting external interrupt active edge

Related register: Interrupt edge selection register (address 3A16)

Timer X mode register (address 2716)

Timer Y mode register (address 2816)

When switching interrupt sources of an interrupt vector address

where two or more interrupt sources are allocated

Related register: A-D control regsiter (address 3416)

When not requiring for the interrupt occurrence synchronized with

these setting, take the following sequence.

Set the corresponding interrupt enable bit to “0” (disabled).

Set the interrupt edge select bit or the interrupt source select bit

to “1”.

Set the corresponding interrupt request bit to “0” after 1 or more

instructions have been executed.

Set the corresponding interrupt enable bit to “1” (enabled).

Notes1: Vector addresses contain interrupt jump destination addresses.

2: Reset function in the same way as an interrupt with the highest priority.

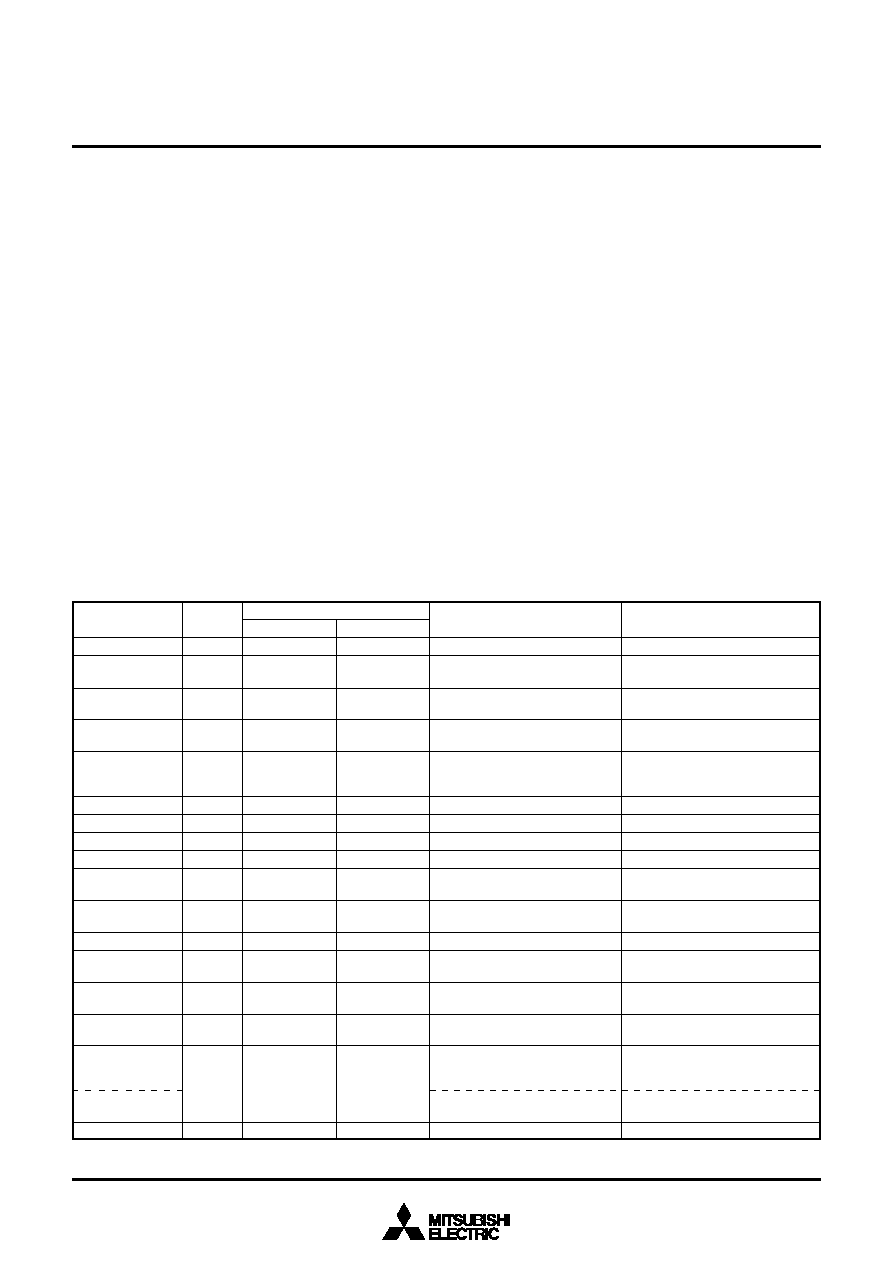

Table 10 Interrupt vector addresses and priority

Remarks

Interrupt Request

Generating Conditions

At reset

At detection of either rising or

falling edge of INT0 input

At detection of either rising or

falling edge of INT1 input

At completion of serial I/O data

reception

At completion of serial I/O trans-

mit shift or when transmission

buffer is empty

Interrupt Source

Low

High

Priority

Vector Addresses (Note 1)

Reset (Note 2)

INT0

INT1

Serial I/O

reception

Serial I/O

transmission

Timer X

Timer Y

Timer 2

Timer 3

CNTR0

CNTR1

Timer 1

INT2

INT3

Key input

(Key-on wake-up)

ADT

A-D conversion

BRK instruction

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

FFFD16

FFFB16

FFF916

FFF716

FFF516

FFF316

FFF116

FFEF16

FFED16

FFEB16

FFE916

FFE716

FFE516

FFE316

FFE116

FFDF16

FFDD16

FFFC16

FFFA16

FFF816

FFF616

FFF416

FFF216

FFF016

FFEE16

FFEC16

FFEA16

FFE816

FFE616

FFE416

FFE216

FFE016

FFDE16

FFDC16

At timer X underflow

At timer Y underflow

At timer 2 underflow

At timer 3 underflow

At detection of either rising or

falling edge of CNTR0 input

At detection of either rising or

falling edge of CNTR1 input

At timer 1 underflow

At detection of either rising or

falling edge of INT2 input

At detection of either rising or

falling edge of INT3 input

At falling of conjunction of input

level for port P2 (at input mode)

At falling of ADT input

At completion of A-D conversion

At BRK instruction execution

Non-maskable

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

Valid when serial I/O is selected

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(active edge selectable)

External interrupt

(Valid at falling)

Valid when ADT interrupt is se-

lected, External interrupt

(Valid at falling)

Valid when A-D interrupt is se-

lected

Non-maskable software interrupt

相关PDF资料 |

PDF描述 |

|---|---|

| M38223MAXXXHP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38224MCMFP | 50000 SYSTEM GATE 2.5 VOLT FPGA - NOT RECOMMENDED for NEW DESIGN |

| M38224E1FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38224E1FS | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38224MCMFS | 50000 SYSTEM GATE 2.5 VOLT FPGA - NOT RECOMMENDED for NEW DESIGN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M38224M6A-376HP#U0 | 制造商:Renesas Electronics Corporation 功能描述: |

| M38224M6A-383HP#U0 | 制造商:Renesas Electronics Corporation 功能描述: |

| M38227ECFP | 功能描述:IC 740 MCU EPROM 48K 80QFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:740/38000 产品培训模块:CAN Basics Part-1 CAN Basics Part-2 Electromagnetic Noise Reduction Techniques Part 1 M16C Product Overview Part 1 M16C Product Overview Part 2 标准包装:1 系列:M16C™ M32C/80/87 核心处理器:M32C/80 芯体尺寸:16/32-位 速度:32MHz 连通性:EBI/EMI,I²C,IEBus,IrDA,SIO,UART/USART 外围设备:DMA,POR,PWM,WDT 输入/输出数:121 程序存储器容量:384KB(384K x 8) 程序存储器类型:闪存 EEPROM 大小:- RAM 容量:24K x 8 电压 - 电源 (Vcc/Vdd):3 V ~ 5.5 V 数据转换器:A/D 34x10b,D/A 2x8b 振荡器型:内部 工作温度:-20°C ~ 85°C 封装/外壳:144-LQFP 包装:托盘 产品目录页面:749 (CN2011-ZH PDF) 配用:R0K330879S001BE-ND - KIT DEV RSK M32C/87 |

| M38227ECFP#U0 | 功能描述:MCU 3/5V 48K PB-FREE 80-QFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:740/38000 标准包装:250 系列:56F8xxx 核心处理器:56800E 芯体尺寸:16-位 速度:60MHz 连通性:CAN,SCI,SPI 外围设备:POR,PWM,温度传感器,WDT 输入/输出数:21 程序存储器容量:40KB(20K x 16) 程序存储器类型:闪存 EEPROM 大小:- RAM 容量:6K x 16 电压 - 电源 (Vcc/Vdd):2.25 V ~ 3.6 V 数据转换器:A/D 6x12b 振荡器型:内部 工作温度:-40°C ~ 125°C 封装/外壳:48-LQFP 包装:托盘 配用:MC56F8323EVME-ND - BOARD EVALUATION MC56F8323 |

| M38227ECFS | 制造商:Renesas Electronics Corporation 功能描述:MCU 8BIT 740 CISC 48KB EPROM 5V 80CLCC - Bulk |

发布紧急采购,3分钟左右您将得到回复。