- 您现在的位置:买卖IC网 > PDF目录370932 > M38271M4MXXXHP (Mitsubishi Electric Corporation) Single, Low Power, Rail-to-Rail Input/Output Operational Amplifier w/Shutdown 8-PDIP -40 to 125 PDF资料下载

参数资料

| 型号: | M38271M4MXXXHP |

| 厂商: | Mitsubishi Electric Corporation |

| 英文描述: | Single, Low Power, Rail-to-Rail Input/Output Operational Amplifier w/Shutdown 8-PDIP -40 to 125 |

| 中文描述: | 单芯片8位CMOS微机 |

| 文件页数: | 56/70页 |

| 文件大小: | 1112K |

| 代理商: | M38271M4MXXXHP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页当前第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页

56

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

3827 Group

MITSUBISHI MICROCOMPUTERS

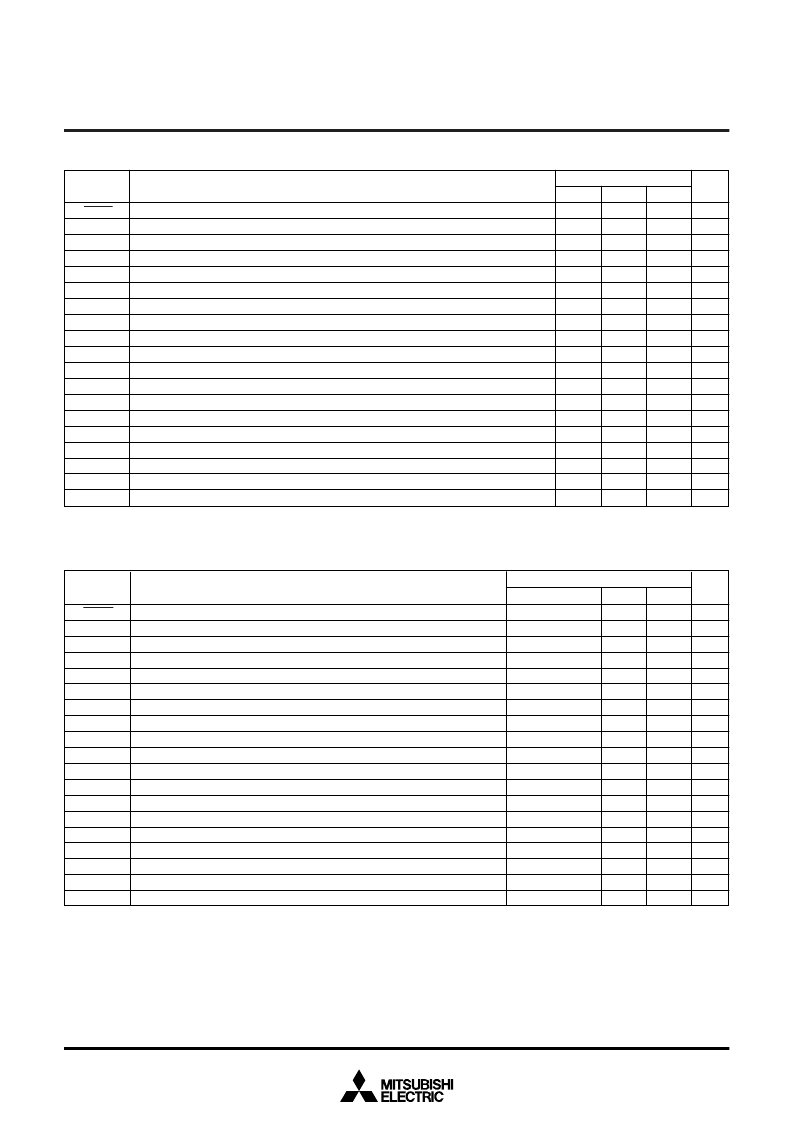

Table 20 Timing requirements 1

(V

CC

= 4.0 to 5.5 V, V

SS =

0 V, Ta = –20 to 85

°

C, unless otherwise noted)

2

125

45

40

250

105

105

80

80

800

370

370

220

100

1000

400

400

200

200

Note:

When bit 6 of address 001A

16

is “1”.

Divide this value by four when bit 6 of address 001A

16

is “0”.

Reset input “L” pulse width

Main clock input cycle time (X

IN

input)

Main clock input “H” pulse width

Main clock input “L” pulse width

CNTR

0

, CNTR

1

input cycle time

CNTR

0

, CNTR

1

input “H” pulse width

CNTR

0

, CNTR

1

input “L” pulse width

INT

0

to INT

2

input “H” pulse width

INT

0

to INT

2

input “L” pulse width

Serial I/O1 clock input cycle time

(Note)

Serial I/O1 clock input “H” pulse width

(Note)

Serial I/O1 clock input “L” pulse width

(Note)

Serial I/O1 input set up time

Serial I/O1 input hold time

Serial I/O2 clock input cycle time

(Note)

Serial I/O2 clock input “H” pulse width

(Note)

Serial I/O2 clock input “L” pulse width

(Note)

Serial I/O2 input set up time

Serial I/O2 input hold time

t

w(RESET)

t

c(X

IN

)

t

wH(X

IN

)

t

wL(X

IN

)

t

c(CNTR)

t

wH(CNTR)

t

wL(CNTR)

t

wH(INT)

t

wL(INT)

t

c(S

CLK1

)

t

wH(S

CLK1

)

t

wL(S

CLK1

)

t

su(R

X

D–S

CLK1

)

t

h(S

CLK1

–R

X

D)

t

c(S

CLK2

)

t

wH(S

CLK2

)

t

wL

(S

CLK2

)

t

su(S

IN2

–S

CLK2

)

t

h(S

CLK2

–S

IN2

)

Symbol

Parameter

Limits

Typ.

Min.

μ

s

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Unit

Max.

Table 21 Timing requirements 2

(V

CC

= 2.2 to 4.0 V, V

SS =

0 V, Ta = –20 to 85

°

C, unless otherwise noted)

2

125

45

40

900/(V

CC

–0.4)

t

c(CNTR)

/2–20

t

c(CNTR)

/2–20

230

230

2000

950

950

400

200

2000

950

950

400

300

Reset input “L” pulse width

Main clock input cycle time (X

IN

input)

Main clock input “H” pulse width

Main clock input “L” pulse width

CNTR

0

, CNTR

1

input cycle time

CNTR

0

, CNTR

1

input “H” pulse width

CNTR

0

, CNTR

1

input “L” pulse width

INT

0

to INT

2

input “H” pulse width

INT

0

to INT

2

input “L” pulse width

Serial I/O1 clock input cycle time

(Note)

Serial I/O1 clock input “H” pulse width

(Note)

Serial I/O1 clock input “L” pulse width

(Note)

Serial I/O1 input set up time

Serial I/O1 input hold time

Serial I/O2 clock input cycle time

(Note)

Serial I/O2 clock input “H” pulse width

(Note)

Serial I/O2 clock input “L” pulse width

(Note)

Serial I/O2 input set up time

Serial I/O2 input hold time

t

w(RESET)

t

c(X

IN

)

t

wH(X

IN

)

t

wL(X

IN

)

t

c(CNTR)

t

wH(CNTR)

t

wL(CNTR)

t

wH(INT)

t

wL(INT)

t

c(S

CLK1

)

t

wH(S

CLK1

)

t

wL(S

CLK1

)

t

su(R

X

D–S

CLK1

)

t

h(S

CLK1

–R

X

D)

t

c(S

CLK2

)

t

wH(S

CLK2

)

t

wL(S

CLK2

)

Symbol

Parameter

Limits

Min.

μ

s

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Unit

Typ.

Max.

Note:

When bit 6 of address 001A

16

is “1”.

Divide this value by four when bit 6 of address 001A

16

is “0”.

t

su(S

IN2

–S

CLK2

)

t

h(S

CLK2

–S

IN2

)

相关PDF资料 |

PDF描述 |

|---|---|

| M38271M5MXXXGP | Single, Low Power, Rail-to-Rail Input/Output Operational Amplifier w/Shutdown 8-PDIP -40 to 125 |

| M38271M5MXXXHP | Single, Low Power, Rail-to-Rail Input/Output Operational Amplifier w/Shutdown 8-SOIC -40 to 125 |

| M38271M6MXXXFP | Single, Low Power, Rail-to-Rail Input/Output Operational Amplifier w/Shutdown 8-SOIC -40 to 125 |

| M38271M6MXXXFS | Single, Low Power, Rail-to-Rail Input/Output Operational Amplifier w/Shutdown 8-TSSOP -40 to 125 |

| M38271M6MXXXGP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M3828 BK001 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 1000' |

| M3828 BK002 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 500' |

| M3828 BK005 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 100' |

| M3828 BK199 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 3000=3000' |

| M3829 BK001 | 制造商:Alpha Wire Company 功能描述:CBL 4COND 16AWG BLK 1000' |

发布紧急采购,3分钟左右您将得到回复。