- 您现在的位置:买卖IC网 > PDF目录180211 > M4-128/64-12VC (LATTICE SEMICONDUCTOR CORP) High Performance E 2 CMOS In-System Programmable Logic PDF资料下载

参数资料

| 型号: | M4-128/64-12VC |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | High Performance E 2 CMOS In-System Programmable Logic |

| 中文描述: | EE PLD, 12 ns, PQFP100 |

| 封装: | TQFP-100 |

| 文件页数: | 11/46页 |

| 文件大小: | 754K |

| 代理商: | M4-128/64-12VC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

MACH 4 Family

19

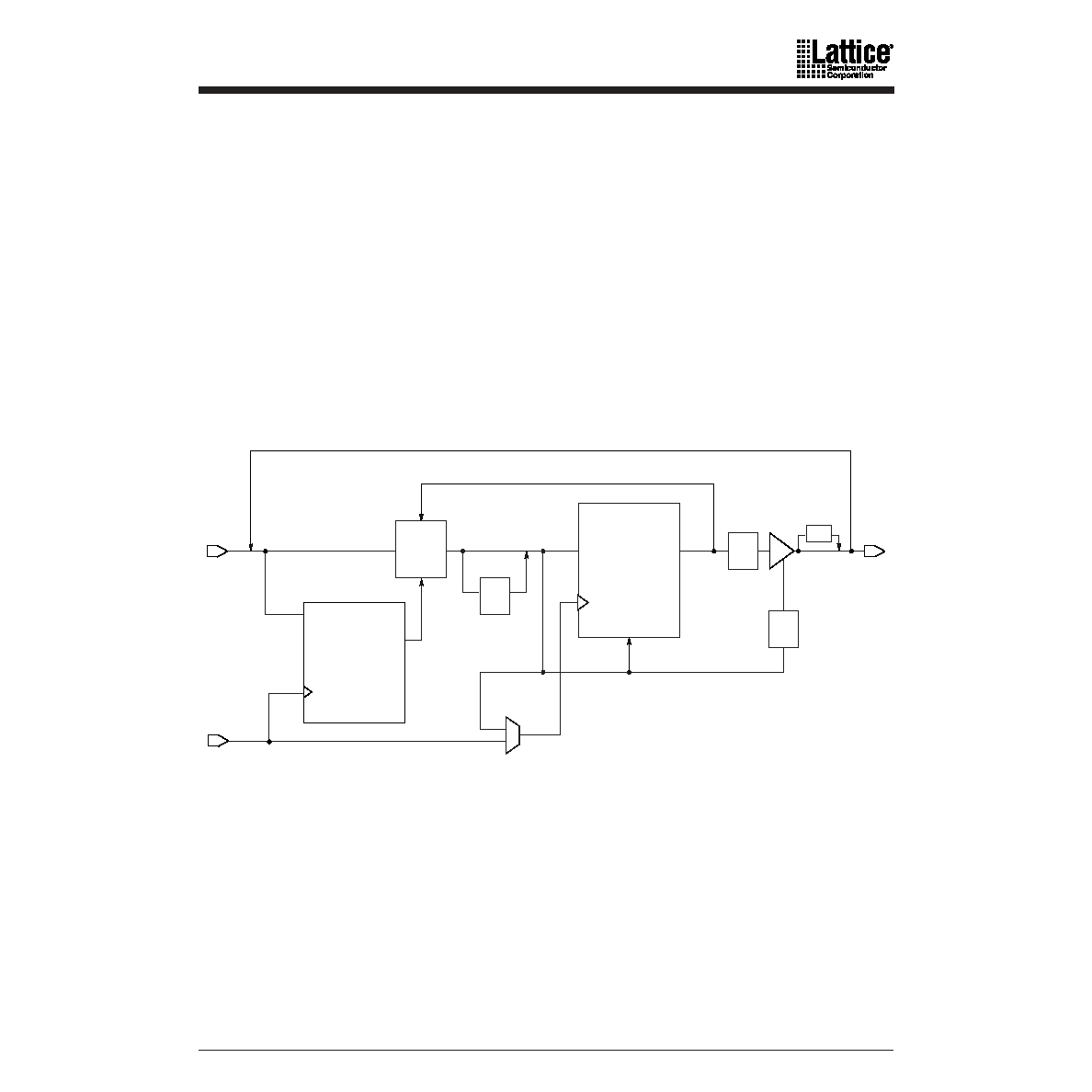

MACH 4 TIMING MODEL

The primary focus of the MACH 4 timing model is to accurately represent the timing in a MACH

4 device, and at the same time, be easy to understand. This model accurately describes all

combinatorial and registered paths through the device, making a distinction between internal

feedback and external feedback. A signal uses internal feedback when it is fed back into the

switch matrix or block without having to go through the output buffer. The input register

specications are also reported as internal feedback. When a signal is fed back into the switch

matrix after having gone through the output buffer, it is using external feedback.

The parameter, tBUF, is dened as the time it takes to go from feedback through the output buffer

to the I/O pad. If a signal goes to the internal feedback rather than to the I/O pad, the parameter

designator is followed by an “i”. By adding tBUF to this internal parameter, the external parameter

is derived. For example, tPD = tPDi + tBUF. A diagram representing the modularized MACH 4

timing model is shown in Figure 15. Refer to the Technical Note entitled MACH 4 Timing and

High Speed Design for a more detailed discussion about the timing parameters.

SPEEDLOCKING FOR GUARANTEED FIXED TIMING

The MACH 4 architecture allows allocation of up to 20 product terms to an individual macrocell

with the assistance of an XOR gate without incurring additional timing delays.

The design of the switch matrix and PAL blocks guarantee a xed pin-to-pin delay that is

independent of the logic required by the design. Other competitive CPLDs incur serious timing

delays as product terms expand beyond their typical 4 or 5 product term limits. Speed and

SpeedLocking combine to give designs easy access to the performance required in today’s

designs.

(External Feedback)

(Internal Feedback)

INPUT REG/

INPUT LATCH

tSIRS

tHIRS

tSIL

tHIL

tSIRZ

tHIRZ

tSILZ

tHILZ

tPDILi

tICOSi

tIGOSi

tPDILZi

Q

tSS(T)

tSA(T)

tH(S/A)

tS(S/A)L

tH(S/A)L

tSRR

tPDi

tPDLi

tCO(S/A)i

tGO(S/A)i

tSRi

COMB/DFF/TFF/

LATCH/SR*/JK*

S/R

IN

BLK CLK

OUT

tPL

tBUF

tEA

tER

tSLW

Q

Central

Switch

Matrix

*emulated

17466G-025

Figure 15. MACH 4 Timing Model

相关PDF资料 |

PDF描述 |

|---|---|

| M4-128/64-12VI | High Performance E 2 CMOS In-System Programmable Logic |

| M4-128/64-12YC | High Performance E 2 CMOS In-System Programmable Logic |

| M4-128/64-12YI | High Performance E 2 CMOS In-System Programmable Logic |

| M4-128/64-15VC | High Performance E 2 CMOS In-System Programmable Logic |

| M4-128/64-15YC | High Performance E 2 CMOS In-System Programmable Logic |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M4-128N/64-10JC | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M4-128N/64-10JI | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M4-128N/64-12JC | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M4-128N/64-12JI | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M4-128N/64-14JI | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。