- 您现在的位置:买卖IC网 > PDF目录180211 > M4-128/64-12VI (LATTICE SEMICONDUCTOR CORP) High Performance E 2 CMOS In-System Programmable Logic PDF资料下载

参数资料

| 型号: | M4-128/64-12VI |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | High Performance E 2 CMOS In-System Programmable Logic |

| 中文描述: | EE PLD, 12 ns, PQFP100 |

| 封装: | TQFP-100 |

| 文件页数: | 4/46页 |

| 文件大小: | 754K |

| 代理商: | M4-128/64-12VI |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页

12

MACH 4 Family

Note:

1. Polarity of CLK/LE can be programmed

Although the macrocell shows only one input to the register, the XOR gate in the logic allocator

allows the D-, T-type register to emulate J-K, and S-R behavior. In this case, the available product

terms are divided between J and K (or S and R). When congured as J-K, S-R, or T-type, the

extra product term must be used on the XOR gate input for ip-op emulation. In any register

type, the polarity of the inputs can be programmed.

The clock input to the ip-op can select any of the four PAL block clocks in synchronous mode,

with the additional choice of either polarity of an individual product term clock in the

asynchronous mode.

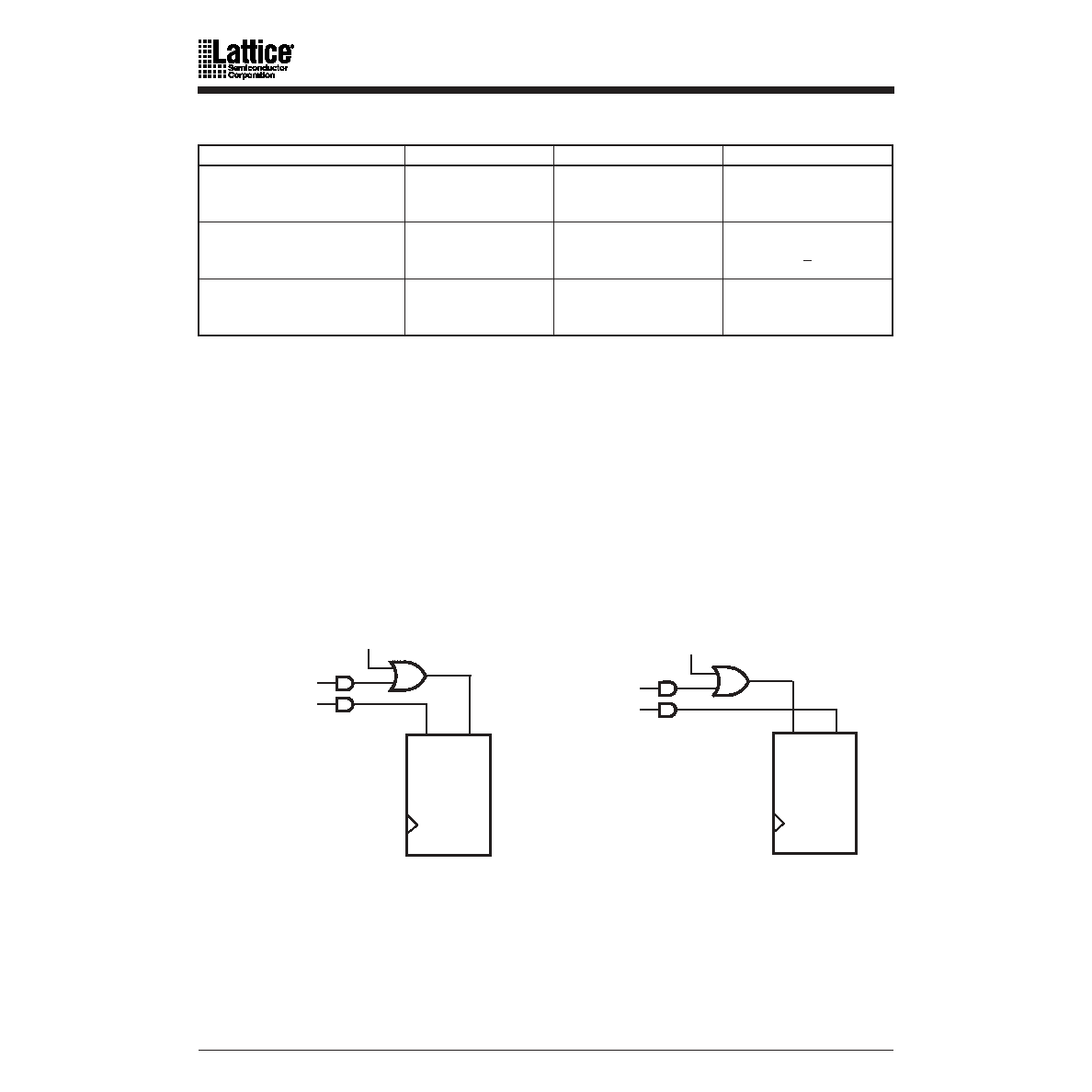

The initialization circuit depends on the mode. In synchronous mode (Figure 7), asynchronous

reset and preset are provided, each driven by a product term common to the entire PAL block.

Table 8. Register/Latch Operation

Conguration

Input(s)

CLK/LE 1

Q+

D-type Register

D=X

D=0

D=1

0,1, ↓ (↑)

↑ (↓)

Q

0

1

T-type Register

T=X

T=0

T=1

0, 1, ↓ (↑)

↑ (↓)

Q

D-type Latch

D=X

D=0

D=1

1(0)

0(1)

Q

0

1

Power-Up

Reset

AP

D/T/L

AR

Q

PAL-Block

Initialization

Product Terms

a. Power-up reset

Power-Up

Preset

AP

D/L

PAL-Block

Initialization

Product Terms

AR

Q

17466G-012

17466G-013

Figure 7. Synchronous Mode Initialization Congurations

b. Power-up preset

相关PDF资料 |

PDF描述 |

|---|---|

| M4-128/64-12YC | High Performance E 2 CMOS In-System Programmable Logic |

| M4-128/64-12YI | High Performance E 2 CMOS In-System Programmable Logic |

| M4-128/64-15VC | High Performance E 2 CMOS In-System Programmable Logic |

| M4-128/64-15YC | High Performance E 2 CMOS In-System Programmable Logic |

| M4-128/64-18VI | High Performance E 2 CMOS In-System Programmable Logic |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M4-128N/64-10JC | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M4-128N/64-10JI | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M4-128N/64-12JC | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M4-128N/64-12JI | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M4-128N/64-14JI | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。