- 您现在的位置:买卖IC网 > PDF目录180212 > M4-128/64-15YC (LATTICE SEMICONDUCTOR CORP) High Performance E 2 CMOS In-System Programmable Logic PDF资料下载

参数资料

| 型号: | M4-128/64-15YC |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | High Performance E 2 CMOS In-System Programmable Logic |

| 中文描述: | EE PLD, 15 ns, PQFP100 |

| 封装: | PLASTIC, QFP-100 |

| 文件页数: | 42/46页 |

| 文件大小: | 754K |

| 代理商: | M4-128/64-15YC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页当前第42页第43页第44页第45页第46页

MACH 4 Family

5

FUNCTIONAL DESCRIPTION

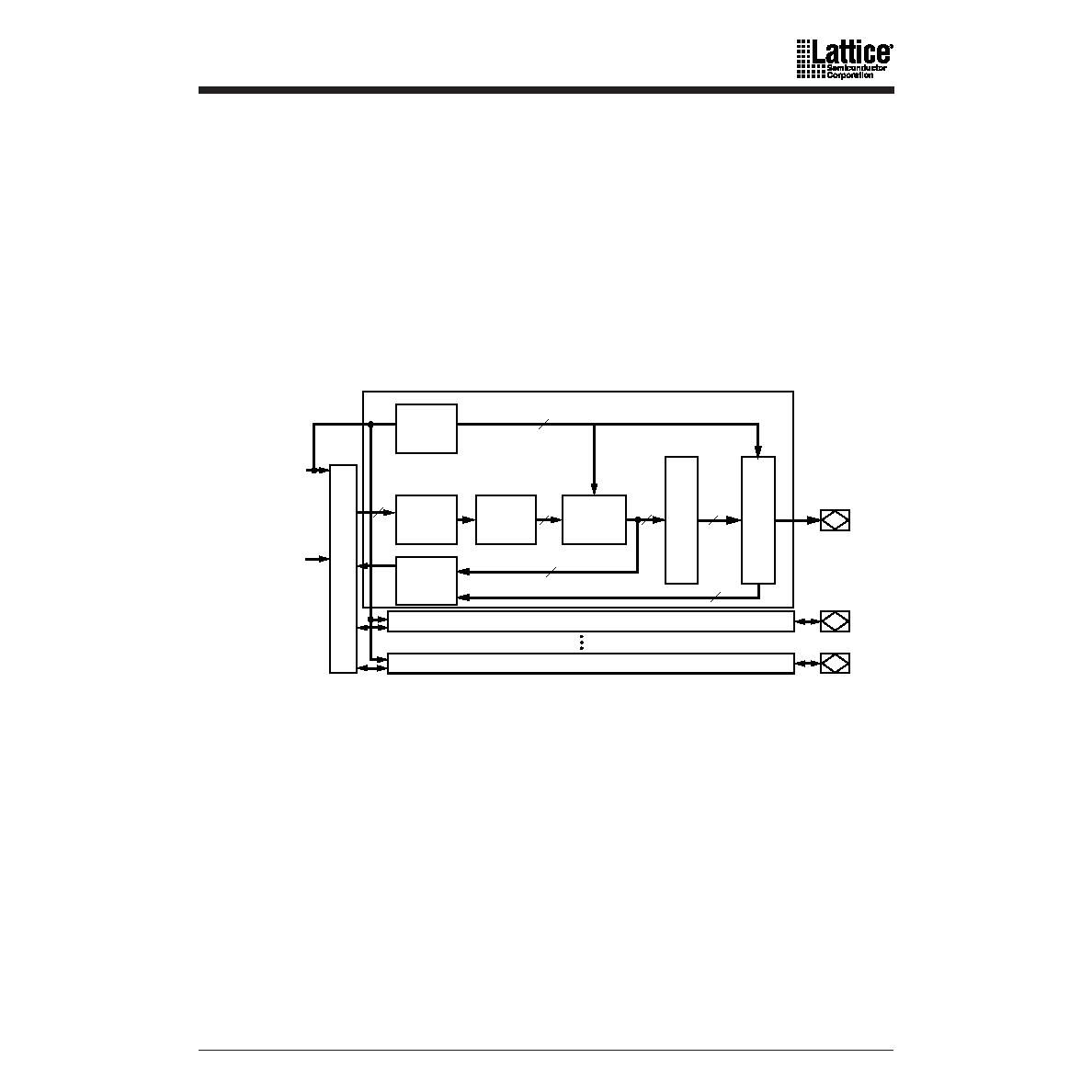

The fundamental architecture of MACH 4 devices (Figure 1) consists of multiple, optimized PAL

blocks interconnected by a central switch matrix. The central switch matrix allows

communication between PAL blocks and routes inputs to the PAL blocks. Together, the PAL

blocks and central switch matrix allow the logic designer to create large designs in a single

device instead of having to use multiple devices.

The key to being able to make effective use of these devices lies in the interconnect schemes.

In MACH 4 architecture, the macrocells are exibly coupled to the product terms through the

logic allocator, and the I/O pins are exibly coupled to the macrocells due to the output switch

matrix. In addition, more input routing options are provided by the input switch matrix. These

resources provide the exibility needed to t designs efciently.

Notes:

1. 16 for MACH 4 devices with 1:1 macrocell-I/O cell ratio (see next page).

2. Block clocks do not go to I/O cells in M4(LV)-32/32.

3. M4(LV)-192/96 and M4(LV)-256/128 have dedicated clock pins which cannot be used as inputs and do not connect to the central

switch matrix.

I/O

Pins

Clock/Input

Pins

Central

Switch

Matrix

I/O

Pins

I/O

Pins

Dedicated

Input Pins

PAL Block

Logic

Allocator

with XOR

Output/

Buried

Macrocells

33/

34/

36

16

Clock

Generator

Logic

Array

Output

Switch

Matrix

Input

Switch

Matrix

I/O

Cells

16

8

Note 1

Note 2

Note 3

4

PAL Block

17466G-001

Figure 1. MACH 4 Block Diagram and PAL Block Structure

相关PDF资料 |

PDF描述 |

|---|---|

| M4-128/64-18VI | High Performance E 2 CMOS In-System Programmable Logic |

| M4-128/64-18YI | High Performance E 2 CMOS In-System Programmable Logic |

| M4-128/64-7VC | High Performance E 2 CMOS In-System Programmable Logic |

| M4-128/64-7YC | High Performance E 2 CMOS In-System Programmable Logic |

| M4-128N/64-10JC | High Performance E 2 CMOS In-System Programmable Logic |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M4-128N/64-10JC | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M4-128N/64-10JI | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M4-128N/64-12JC | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M4-128N/64-12JI | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M4-128N/64-14JI | 功能描述:CPLD - 复杂可编程逻辑器件 Use ispMACH 4000V or M4A5 RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。