- 您现在的位置:买卖IC网 > PDF目录383302 > M470T2953CZ0 (SAMSUNG SEMICONDUCTOR CO. LTD.) DDR2 Unbuffered SODIMM PDF资料下载

参数资料

| 型号: | M470T2953CZ0 |

| 厂商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | DDR2 Unbuffered SODIMM |

| 中文描述: | 无缓冲DDR2内存的SODIMM |

| 文件页数: | 10/20页 |

| 文件大小: | 270K |

| 代理商: | M470T2953CZ0 |

Rev. 1.1 Mar. 2005

256MB, 512MB, 1GB Unbuffered SODIMMs

DDR2 SDRAM

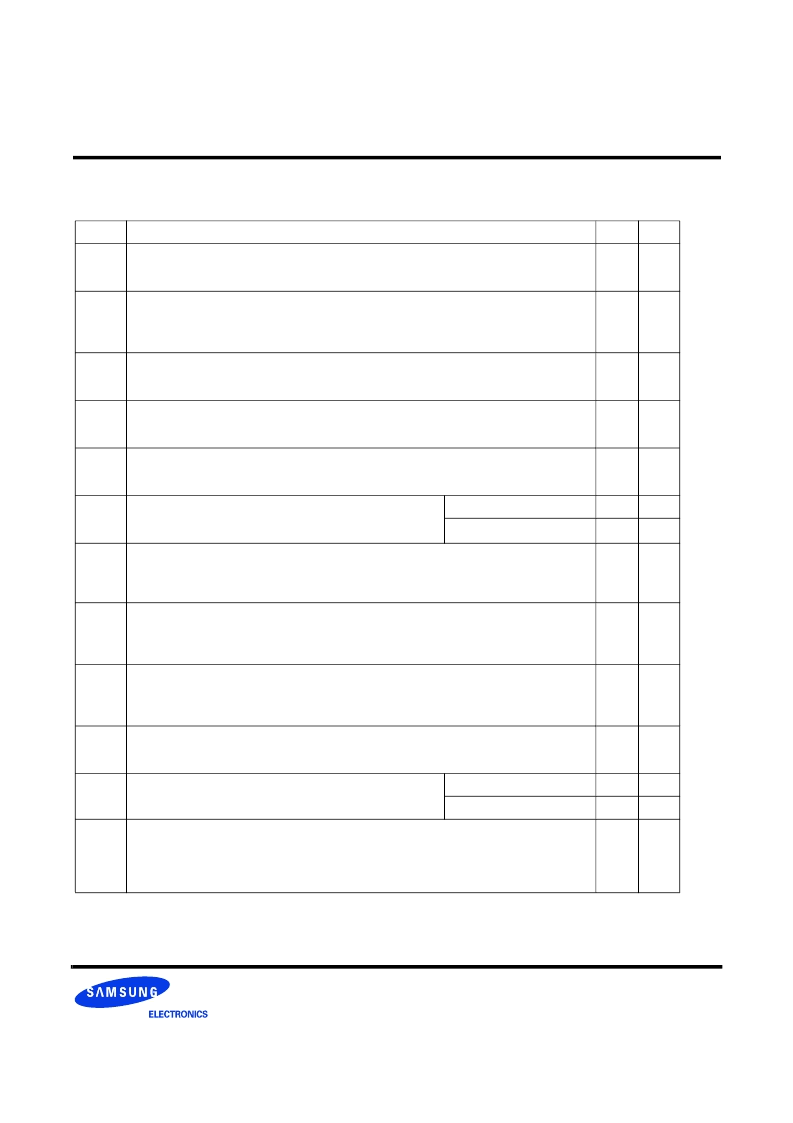

IDD Specification Parameters Definition

(IDD values are for full operating range of Voltage and Temperature)

Symbol

Proposed Conditions

Units

Notes

IDD0

Operating one bank active-precharge current

;

tCK = tCK(IDD), tRC = tRC(IDD), tRAS = tRASmin(IDD); CKE is HIGH, CS\ is HIGH between valid com-

mands; Address bus inputs are SWITCHING; Data bus inputs are SWITCHING

mA

IDD1

Operating one bank active-read-precharge current

;

IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRC = tRC (IDD), tRAS = tRASmin(IDD), tRCD

= tRCD(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address businputs are SWITCHING;

Data pattern is same as IDD4W

mA

IDD2P

Precharge power-down current

;

All banks idle; tCK = tCK(IDD); CKE is LOW; Other control and address bus inputs are STABLE; Data bus

inputs are FLOATING

mA

IDD2Q

Precharge quiet standby current

;

All banks idle; tCK = tCK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputsare STA-

BLE; Data bus inputs are FLOATING

mA

IDD2N

Precharge standby current

;

All banks idle; tCK = tCK(IDD); CKE is HIGH, CS\ is HIGH; Other control and address bus inputs are

SWITCHING; Data bus inputs are SWITCHING

mA

IDD3P

Active power-down current

;

All banks open; tCK = tCK(IDD); CKE is LOW; Other control and

address bus inputs are STABLE; Data bus inputs are FLOATING

Fast PDN Exit MRS(12) = 0mA

mA

Slow PDN Exit MRS(12) = 1mA

mA

IDD3N

Active standby current

;

All banks open; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP = tRP(IDD); CKE is HIGH, CS\ is HIGH

between valid commands; Other control and address bus inputs are SWITCHING; Data bus inputs are

SWITCHING

mA

IDD4W

Operating burst write current

;

All banks open, Continuous burst writes; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRAS = tRAS-

max(IDD), tRP = tRP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus inputs are

SWITCHING; Data bus inputs are SWITCHING

mA

IDD4R

Operating burst read current

;

All banks open, Continuous burst reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRAS

= tRASmax(IDD), tRP = tRP(IDD); CKE is HIGH, CS\ is HIGH between valid commands; Address bus

inputs are SWITCHING; Data pattern is same as IDD4W

mA

IDD5B

Burst auto refresh current

;

tCK = tCK(IDD); Refresh command at every tRFC(IDD) interval; CKE is HIGH, CS\ is HIGH between valid

commands; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING

mA

IDD6

Self refresh current

;

CK and CK\ at 0V; CKE

≤

0.2V; Other control and address bus inputs

are FLOATING; Data bus inputs are FLOATING

Normal

mA

Low Power

mA

IDD7

Operating bank interleave read current

;

All bank interleaving reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = tRCD(IDD)-1*tCK(IDD); tCK =

tCK(IDD), tRC = tRC(IDD), tRRD = tRRD(IDD), tRCD = 1*tCK(IDD); CKE is HIGH, CS\ is HIGH between

valid commands; Address bus inputs are STABLE during DESELECTs; Data pattern is same as IDD4R;

Refer to the following page for detailed timing conditions

mA

相关PDF资料 |

PDF描述 |

|---|---|

| M470T6554CZ0-CC | DDR2 Unbuffered SODIMM |

| M470T2953CZ0-CC | Fuses, 15A 250V CERAMIC LEAD |

| M470T3354CZ0-CD5 | DDR2 Unbuffered SODIMM 200pin Unbuffered SODIMM based on 512Mb C-die 64bit Non-ECC |

| M470T2953CZ0-CD6 | DDR2 Unbuffered SODIMM |

| M470T2953CZ0-D5 | DDR2 Unbuffered SODIMM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M470T2953CZ0-CC | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:DDR2 Unbuffered SODIMM |

| M470T2953CZ0-CCC | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:DDR2 Unbuffered SODIMM 200pin Unbuffered SODIMM based on 512Mb C-die 64bit Non-ECC |

| M470T2953CZ0-CD5 | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:DDR2 Unbuffered SODIMM 200pin Unbuffered SODIMM based on 512Mb C-die 64bit Non-ECC |

| M470T2953CZ0-CD6 | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:DDR2 Unbuffered SODIMM |

| M470T2953CZ0-CE6 | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:DDR2 Unbuffered SODIMM 200pin Unbuffered SODIMM based on 512Mb C-die 64bit Non-ECC |

发布紧急采购,3分钟左右您将得到回复。