- 您现在的位置:买卖IC网 > PDF目录359064 > M48T129VSH (意法半导体) 3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM PDF资料下载

参数资料

| 型号: | M48T129VSH |

| 厂商: | 意法半导体 |

| 元件分类: | DRAM |

| 英文描述: | 3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| 中文描述: | 3.3 - 5V的1兆位的SRAM 128KB的x8计时器 |

| 文件页数: | 12/22页 |

| 文件大小: | 140K |

| 代理商: | M48T129VSH |

M48T129Y, M48T129V

12/22

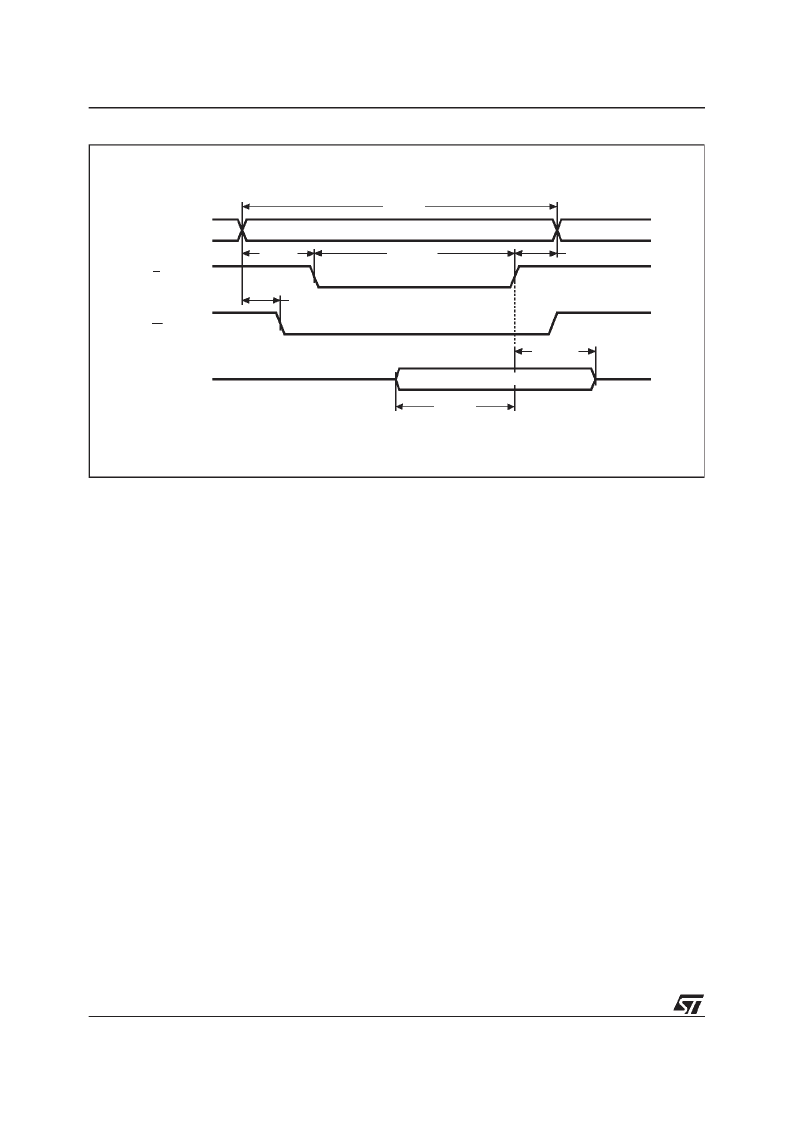

Figure 10. Chip Enable Controlled, Write AC Waveforms

AI02582

tAVAV

tEHAX

tDVWH

A0-A16

E

W

DQ0-DQ7

VALID

tAVEL

tAVWL

tELEH

tWHDX

DATA INPUT

POWER-ON RESET

The M48T129Y/V continuously monitors V

CC

.

When V

CC

falls to the power fail detect trip point,

the RSTpulls low (open drain) and remains low on

power-up for 40 to 200ms after V

CC

passes V

PFD

.

The RSTpin is anopen drainoutput and an appro-

priate pull-up resistor to V

CC

should be chosen to

control the rise time.

CALIBRATING THE CLOCK

The M48T129Y/V is driven by a quartz controlled

oscillator with a nominal frequency of 32,768Hz.

The devices are factory calibrated at 25

°

C and

tested for accuracy. Clock accuracy will not ex-

ceed 35 ppm (parts per million) oscillator frequen-

cy error at 25

°

C, which equates to about * 1.53

minutes per month. When the Calibration circuit is

properly employed, accuracy improves to better

than +4 ppm at 25

°

C. The oscillation rate of crys-

tals changes with temperature. The M48T129Y/V

design employs periodic counter correction. The

calibration circuit adds or subtracts counts from

the oscillator divider circuit at the divide by 256

stage, as shown in Figure 11.

The number of times pulses which are blanked

(subtracted, negative calibration) or split (added,

positive calibration) depends upon the value load-

ed intothe five Calibrationbits foundin theControl

Register. Adding counts speeds the clock up, sub-

tracting counts slows the clock down.The Calibra-

tion bits occupy the five lower orderbits (D4-D0)in

the Control Register 1FFF8h. These bits can be

set to represent any value between 0 and 31 in bi-

nary form. Bit D5 is a Sign bit; ’1’indicates positive

calibration, ’0’ indicates negative calibration. Cali-

bration occurs within a 64 minute cycle. The first

62 minutes in the cycle may, once per minute,

have one second either shortened by 128 or

lengthened by 256 oscillator cycles. If a binary ’1’

is loaded into the register, only the first 2 minutes

in the 64 minute cycle will be modified; if a binary

6 is loaded, the first 12 will be affected, and so on.

Therefore, each calibration step has the effect of

adding 512 or subtracting 256 oscillator cycles for

every 125, 829, 120 actual oscillator cycles, that is

+4.068 or –2.034 ppm of adjustment per calibra-

tion step in the calibration register. Assuming that

the oscillator is running at exactly 32,768Hz, each

of the 31 increments in the Calibration byte would

represent +10.7 or –5.35 seconds per month

which correspondsto a total range of+5.5 or –2.75

minutes per month. Figure 11 illustrates a TIME-

KEEPER calibration waveform.

Two methods are available for ascertaining how

much calibration a given M48T129Y/V may re-

quire. The first involves setting the clock, letting it

run for a month and comparing it to a known accu-

rate reference and recordingdeviation over a fixed

period of time.

相关PDF资料 |

PDF描述 |

|---|---|

| M48T212A | 3.3V TIMEKEEPER CONTROLLER |

| M48T212AMH | 3.3V TIMEKEEPER CONTROLLER |

| M48T212A-85MH6TR | 3.3V TIMEKEEPER CONTROLLER |

| M48T212A-85MH6 | 3.3V TIMEKEEPER CONTROLLER |

| M48T212A-85MH1TR | 3.3V TIMEKEEPER CONTROLLER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M48T129Y | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3V, 1 Mbit (128 Kbit x 8) TIMEKEEPER SRAM |

| M48T129Y_05 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3V, 1 Mbit (128 Kbit x 8) TIMEKEEPER SRAM |

| M48T129Y_10 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3 V, 1 Mbit (128 Kbit x 8) TIMEKEEPER?? SRAM |

| M48T129Y-70CS1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T129Y-70PM1 | 功能描述:实时时钟 1M (128Kx8) 70ns RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。