- 您现在的位置:买卖IC网 > PDF目录359064 > M48T129Y-70PM1 (意法半导体) 3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM PDF资料下载

参数资料

| 型号: | M48T129Y-70PM1 |

| 厂商: | 意法半导体 |

| 元件分类: | DRAM |

| 英文描述: | 3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| 中文描述: | 3.3 - 5V的1兆位的SRAM 128KB的x8计时器 |

| 文件页数: | 15/22页 |

| 文件大小: | 140K |

| 代理商: | M48T129Y-70PM1 |

15/22

M48T129Y, M48T129V

Table 12. Alarm Repeat Modes

RPT4

RPT3

RPT2

RPT1

Alarm Activated

1

1

1

1

Once per Second

1

1

1

0

Once per Minute

1

1

0

0

Once per Hour

1

0

0

0

Once per Day

1

0

0

0

Once per Month

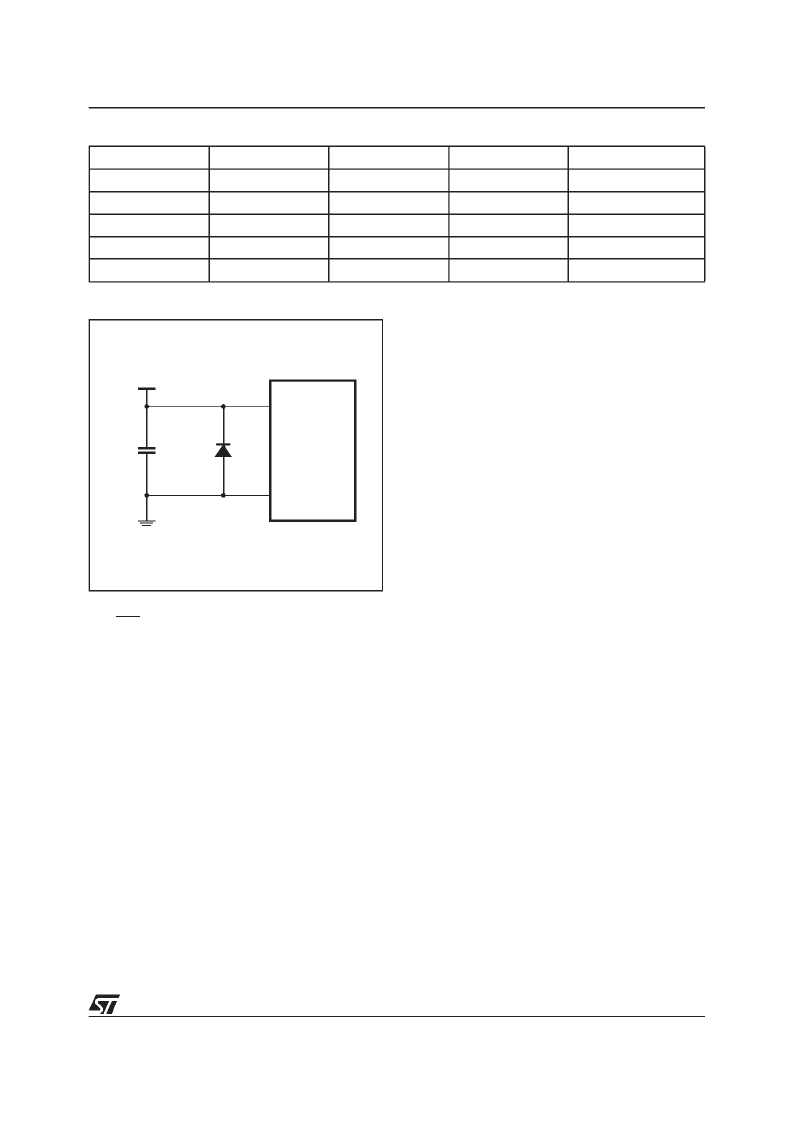

Figure 14. Supply Voltage Protection

AI02169

VCC

0.1

μ

F

DEVICE

VCC

VSS

The IRQ/FT pin is an open drain output which re-

quires a pull-up resistor to V

CC

for proper opera-

tion. A 500-10k resistor is recommended in order

to control the rise time. The FT bit is cleared on

power-up.

BATTERY LOW WARNING

The M48T129Y/V automatically performs battery

voltage monitoring upon power-up and at factory-

programmed time intervals of approximately 24

hours. The Battery Low (BL) bit, Bit D4 of Flags

Register 1FFF0h, will be asserted if the battery

voltage is found to be less than approximately

2.5V.

If a battery lowis generated during a power-up se-

quence, this indicates that the batteryis belowap-

proximately 2.5 volts and may not be able to

maintain data integrity in the SRAM. Data should

be considered suspect and verified as correct.

If a battery low indication is generated during the

24-hour interval check, this indicates that the bat-

tery is near end of life. However, data is not com-

promised due to the fact that a nominal V

CC

is

supplied.

The M48T129Y/V only monitors the battery when

a nominal V

CC

isapplied to the device. Thus appli-

cations which require extensive durations in the

battery back-up modeshould be powered-up peri-

odically (at least once every few months) in order

for this technique to be beneficial. Additionally, if a

battery low is indicated, data integrity should be

verified upon power-up via a checksum or other

technique.

POWER-ON DEFAULTS

Upon application of power to the device, the fol-

lowing register bits are set to a ’0’ state: WDS,

BMB0-BMB4, RB0,RB1, AFE, ABE, W, R and FT.

POWER SUPPLY DECOUPLING

and UNDERSHOOT PROTECTION

I

CC

transients, including those produced by output

switching, can produce voltage fluctuations, re-

sulting in spikes on the V

CC

bus. These transients

can be reduced if capacitors are used to store en-

ergy, which stabilizes the V

CC

bus. The energy

stored in the bypass capacitors will be released as

low going spikes are generated or energy will be

absorbed when overshoots occur. A ceramic by-

pass capacitor value of 0.1

μ

F (see Figure 14) is

recommended in order to provide the needed fil-

tering. In addition to transients that are caused by

normal SRAM operation, powercycling can gener-

ate negative voltage spikes on V

CC

that drive it to

values below V

SS

by as much as one volt. These

negative spikes can cause data corruption in the

SRAM while in battery backup mode. To protect

from these voltage spikes, ST recommends con-

necting a schottky diodefrom V

CC

toV

SS

(cathode

connected to V

CC

, anode to V

SS

). (Schottky diode

1N5817 is recommended for through hole and

MBRS120T3 is recommended for surfacemount).

相关PDF资料 |

PDF描述 |

|---|---|

| M48T129YPM | 3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T129VPM | 3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T129VSH | 3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T212A | 3.3V TIMEKEEPER CONTROLLER |

| M48T212AMH | 3.3V TIMEKEEPER CONTROLLER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M48T129Y-85CS1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T129Y-85PM1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T129YPM | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T129YSH | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T18 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5V, 64Kbit (8 Kb x 8) TIMEKEEPER㈢ SRAM |

发布紧急采购,3分钟左右您将得到回复。