- 您现在的位置:买卖IC网 > PDF目录45050 > M48T201Y-70MH1F (STMICROELECTRONICS) 1 TIMER(S), REAL TIME CLOCK, PDSO44 PDF资料下载

参数资料

| 型号: | M48T201Y-70MH1F |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 时钟/数据恢复及定时提取 |

| 英文描述: | 1 TIMER(S), REAL TIME CLOCK, PDSO44 |

| 封装: | SNAPHAT, ROHS COMPLIANT, PLASTIC, SOIC-44 |

| 文件页数: | 5/37页 |

| 文件大小: | 311K |

| 代理商: | M48T201Y-70MH1F |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

M48T201Y, M48T201V

Operation

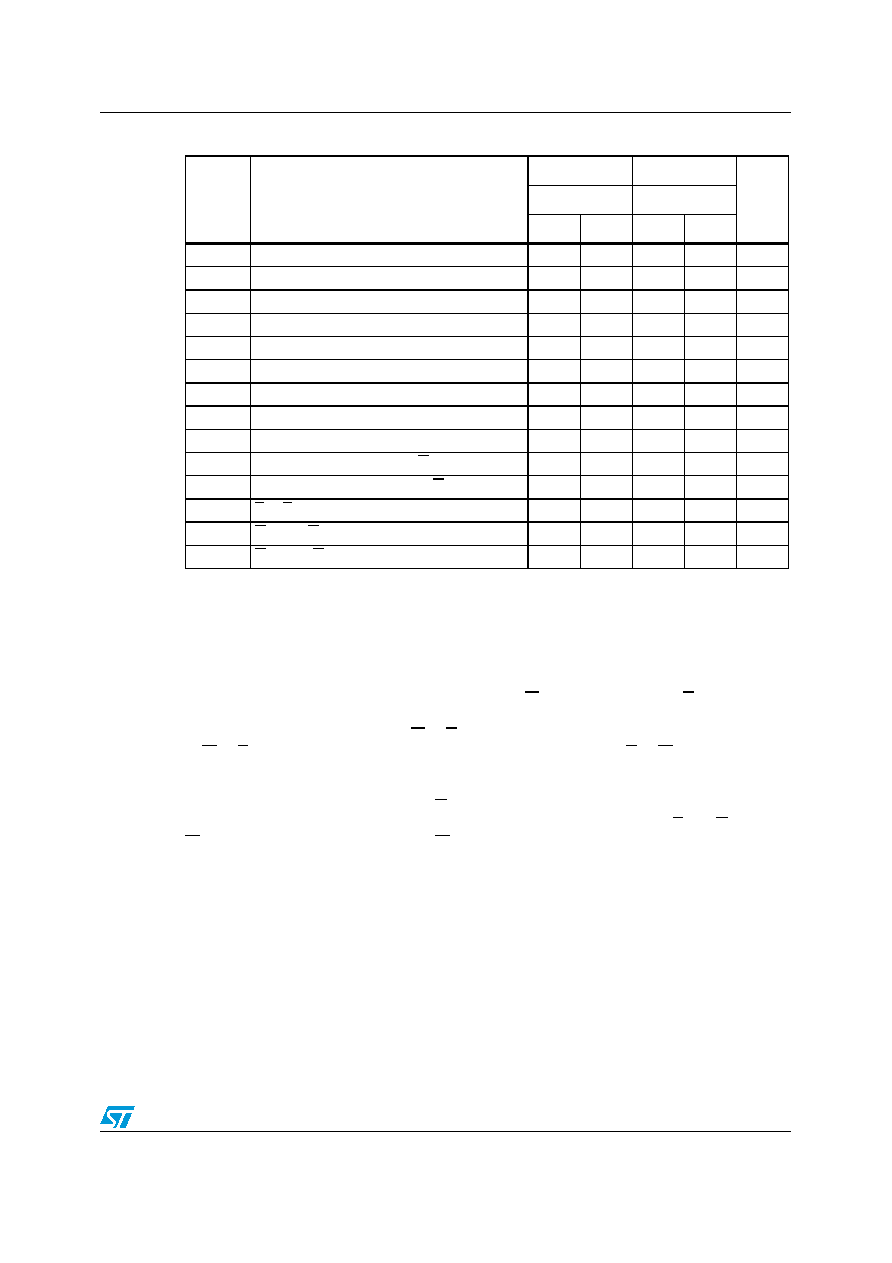

Table 3.

Read mode AC characteristics

2.3

Write mode

The M48T201Y/V is in the WRITE mode whenever W (WRITE enable) and E (chip enable)

are low state after the address inputs are stable. The start of a WRITE is referenced from

the latter occurring falling edge of W or E. A WRITE is terminated by the earlier rising edge

of W or E. The addresses must be held valid throughout the cycle. E or W must return high

for a minimum of tEHAX from chip enable or tWHAX from WRITE enable prior to the initiation

of another READ or WRITE cycle. Data-in must be valid tDVWH prior to the end of WRITE

and remain valid for tWHDX afterward. G should be kept high during WRITE cycles to avoid

bus contention; although, if the output bus has been activated by a low on E and G a low on

W will disable the outputs tWLQZ after W falls.

When the address value presented to the M48T201Y/V during the WRITE is in the range of

7FFFFh-7FFF0h, one of the on-board TIMEKEEPER registers will be selected and data

will be written into the device. When the address value presented to M48T201Y/V is outside

the range of TIMEKEEPER registers, an external SRAM location is selected.

Symbol

Parameter(1)

1.

Valid for ambient operating temperature: TA = 0 to 70°C; VCC = 4.5 to 5.5 V or 3.0 to 3.6 V (except where

noted).

M48T201Y

M48T201V

Unit

–70

–85

Min

Max

Min

Max

tAVAV

READ cycle time

70

85

ns

tAVQV

Address valid to output valid

70

85

ns

tELQV

Chip enable low to output valid

70

85

ns

tGLQV

Output enable low to output valid

25

35

ns

tELQX

(2)

2.

CL = 5 pF.

Chip enable low to output transition

5

ns

tGLQX

Output enable low to output transition

0

ns

tEHQZ

Chip enable high to output Hi-Z

20

25

ns

tGHQZ

Output enable high to output Hi-Z

20

25

ns

tAXQX

Address transition to output transition

5

ns

tAOEL

External SRAM address to GCON low

20

30

ns

tAOEH

Supervisor SRAM address to GCON high

20

30

ns

tEPD

E to ECON low or high

10

15

ns

tOERL

G low to GCON low

15

20

ns

tRO

G high to GCON high

10

15

ns

相关PDF资料 |

PDF描述 |

|---|---|

| M48T201V-85MH1F | 1 TIMER(S), REAL TIME CLOCK, PDSO44 |

| M48T201Y-70MH1 | 1 TIMER(S), REAL TIME CLOCK, PDSO44 |

| M48T201V-85MH1E | 1 TIMER(S), REAL TIME CLOCK, PDSO44 |

| M48T201Y-70MH1E | 1 TIMER(S), REAL TIME CLOCK, PDSO44 |

| M48T201V-85MH6TR | 1 TIMER(S), REAL TIME CLOCK, PDSO44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M48T201Y-70MH1TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3V TIMEKEEPER㈢ supervisor |

| M48T201Y-80MH1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3 V TIMEKEEPER? supervisor |

| M48T201Y-80MH1E | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3 V TIMEKEEPER? supervisor |

| M48T201Y-80MH1F | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3 V TIMEKEEPER? supervisor |

| M48T201Y-80MH1TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3 V TIMEKEEPER? supervisor |

发布紧急采购,3分钟左右您将得到回复。