- 您现在的位置:买卖IC网 > PDF目录359064 > M48T248VPM (意法半导体) 5.0 or 3.3V, 1024K TIMEKEEPER SRAM with PHANTOM PDF资料下载

参数资料

| 型号: | M48T248VPM |

| 厂商: | 意法半导体 |

| 英文描述: | 5.0 or 3.3V, 1024K TIMEKEEPER SRAM with PHANTOM |

| 中文描述: | 5.0或3.3V,1024K与幻象计时器的SRAM |

| 文件页数: | 9/24页 |

| 文件大小: | 306K |

| 代理商: | M48T248VPM |

9/24

M48T248Y, M48T248V

OPERATION MODES

Table 6. Operating Modes

Note: X = V

IH

or V

IL

; V

SO

= Battery Back-up Switchover Voltage

1. See Table 9, page 14 for details.

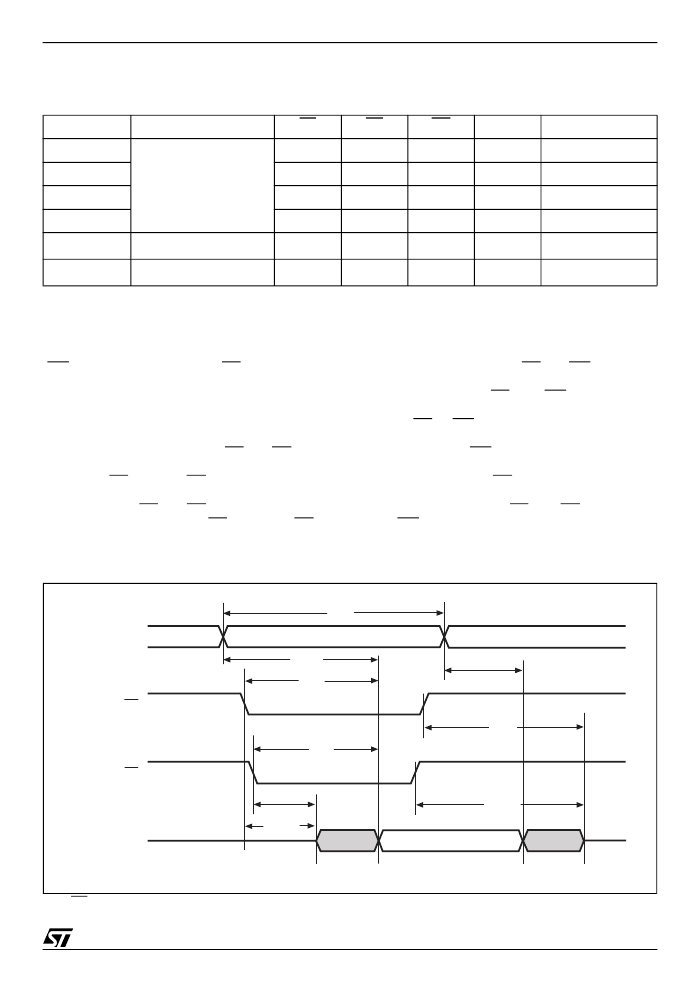

READ

A READ cycle executes whenever WRITE Enable

(WE) is high and Chip Enable (CE) is low (see Fig-

ure 6). The distinct address defined by the 19 ad-

dress inputs (A0-A18) specifies which of the 512K

bytes of data is to be accessed. Valid data will be

accessed by the eight data output drivers within

the specified Access Time (t

ACC

) after the last ad-

dress input signal is stable, the CE and OE access

times, and their respective parameters are satis-

fied. When CE t

ACC

and OE t

ACC

are not satisfied,

then data access times must be measured from

the more recent CE and OE signals, with the limit-

ing parameter being t

CO

(for CE) or t

OE

(for OE) in-

stead of address access.

WRITE

WRITE Mode (see Figure 7, page 10 and Figure 8,

page 11) occurs whenever CE and WE signals are

low (after address inputs are stable). The most re-

cent falling edge of CE and WE will determine

when the WRITE cycle begins (the earlier, rising

edge of CE or WE determines cycle termination).

All address inputs must be kept stable throughout

the WRITE cycle. WE must be high (inactive) for a

minimum recovery time (t

WR

) before a subsequent

cycle is initiated. The OE control signal should be

kept high (inactive) during the WRITE cycles to

avoid bus contention. If CE and OE are low (ac-

tive), WE will disable the outputs for Output Data

WRITE Time (t

ODW

) from its falling edge.

Figure 6. Memory READ Cycle

Note: WE is high for a READ cycle.

Mode

V

CC

CE

OE

WE

DQ7-DQ0

Power

Deselect

4.5V to 5.5V

or

3.0V to 3.6V

V

IH

X

X

High-Z

Standby

WRITE

V

IL

X

V

IL

D

IN

Active

READ

V

IL

V

IL

V

IH

D

OUT

Active

READ

V

IL

V

IH

V

IH

High-Z

Active

Deselect

V

SO

to V

PFD

(min)

(1)

X

X

X

High-Z

CMOS Standby

Deselect

≤

V

SO(1)

X

X

X

High-Z

Battery Back-Up

DQ0 - DQ7

ADDRESSES

OE

CE

DATA OUTPUT

VALID

tOD

tODO

tOE

tRC

tCO

tACC

tCOE

tCOE

tOH

AI04230

相关PDF资料 |

PDF描述 |

|---|---|

| M48T251V-70PM1 | 5.0 or 3.3V, 4096K TIMEKEEPER SRAM with PHANTOM |

| M48T251V-70PM1TR | 5.0 or 3.3V, 4096K TIMEKEEPER SRAM with PHANTOM |

| M48T251V-85PM1 | 5.0 or 3.3V, 4096K TIMEKEEPER SRAM with PHANTOM |

| M48T251V-85PM1TR | 5.0 or 3.3V, 4096K TIMEKEEPER SRAM with PHANTOM |

| M48T251V | 5.0 or 3.3V, 4096K TIMEKEEPER SRAM with PHANTOM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M48T248Y | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3V, 1024K TIMEKEEPER SRAM with PHANTOM |

| M48T248Y-70PM1 | 功能描述:实时时钟 1M (128Kx8) 70ns RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| M48T248Y-70PM1TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3V, 1024K TIMEKEEPER SRAM with PHANTOM |

| M48T248Y-85PM1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3V, 1024K TIMEKEEPER SRAM with PHANTOM |

| M48T248Y-85PM1TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3V, 1024K TIMEKEEPER SRAM with PHANTOM |

发布紧急采购,3分钟左右您将得到回复。