- 您现在的位置:买卖IC网 > PDF目录359066 > M48T59V-70MH6TR (意法半导体) 64 Kbit 8Kb x8 TIMEKEEPER SRAM PDF资料下载

参数资料

| 型号: | M48T59V-70MH6TR |

| 厂商: | 意法半导体 |

| 英文描述: | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| 中文描述: | 64千位8KB的x8 SRAM的计时器 |

| 文件页数: | 10/21页 |

| 文件大小: | 168K |

| 代理商: | M48T59V-70MH6TR |

M48T59, M48T59Y, M48T59V

10/21

condition reset will not occur unless the addresses

are stable at the flag location for at least 15ns

while the divice is in the read mode as shown in

Figure 11.

The IRQ/FT pin is an open drain output and re-

quires a pull-up resistor (10k

recommended) to

V

CC

. The pin remains in the high impedance state

unless an interrupt occurs or the frequency test

mode is enabled.

CLOCK OPERATIONS

Reading the Clock

Updates to the TIMEKEEPER registers should be

halted before clock data is read to prevent reading

data in transition. Because the BiPORT TIME-

KEEPER cells in the RAM array are only data reg-

isters, and not the actual clock counters, updating

the registers can be halted without disturbing the

clock itself.

Updating is halted when a ’1’ is written to the

READ bit, D6 in the Control register (1FF8h). As

long as a ’1’ remains in that position, updating is

halted.

After a halt is issued, the registers reflect the

count; that is, the day, date, and the time that were

current at the moment the halt command was is-

sued.

All of the TIMEKEEPER registers are updated si-

multaneously. A halt will not interrupt an update in

progress. Updating is within a second after the bit

is reset to a ’0’.

Setting the Clock

Bit D7 of the Control register (1FF8h) is the

WRITE bit. Setting the WRITE bit to a ’1’, like the

READ bit, halts updates to the TIMEKEEPER reg-

during the time the device is sampling V

CC

. There-

fore, decoupling of the power supply lines is rec-

ommended.

When V

CC

drops below V

SO

, the control circuit

switches power to the internal battery which pre-

serves data and powers the clock. The internal

button cell will maintain data in the M48T59/59Y/

59V for an accumulated period of at least 7 years

when V

CC

is less than V

SO

. As system power re-

turns and V

CC

rises above V

SO

, the battery is dis-

connected, and the power supply is switched to

external V

CC

. Deselect continues for t

REC

after

V

CC

reaches V

PFD

(max).

For more information on Battery Storage Life refer

to the Application Note AN1012.

POWER-ON RESET

The M48T59/59Y/59V continuously monitors V

CC

.

When V

CC

falls to the power fail detect trip point,

the RST pulls low (open drain) and remains low on

power-up for 40ms to 200ms after V

CC

passes

V

PFD

. RST is valid for all V

CC

conditions. The RST

pin is an open drain output and an appropriate re-

sistor to V

CC

should be chosen to control rise time.

PROGRAMMABLE INTERRUPTS

The M48T59/59Y/59V provides two programma-

ble interrupts; an alarm and a watchdog. When an

interrupt condition occurs, the M48T59/59Y/59V

sets the appropriate flag bit in the flag register

1FF0h. The interrupt enable bits in (AFE and ABE)

in 1FF6h and the Watchdog Steering (WDS) bit in

1FF7h allow the interrupt to activate the IRQ/FT

pin.

The interrupt flags and the IRQ/FT output are

cleared by a read to the flags register. An interrupt

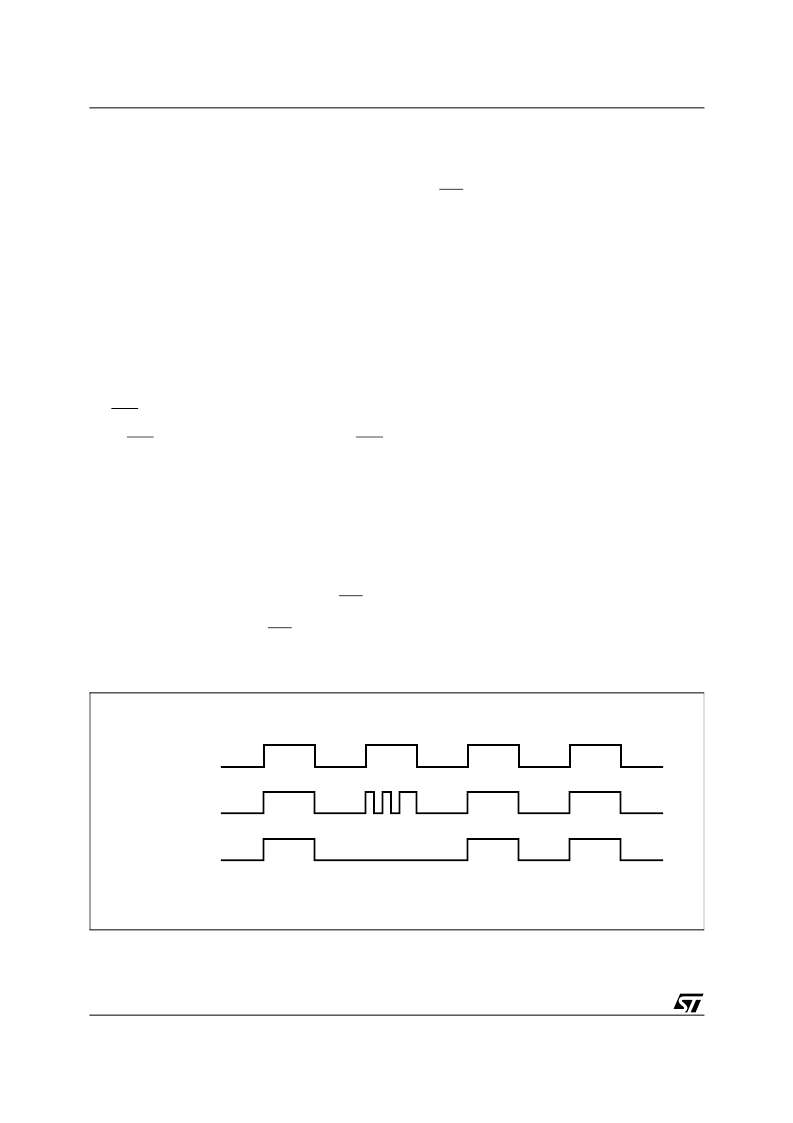

Figure 9. Clock Calibration

AI00594B

NORMAL

POSITIVE

CALIBRATION

NEGATIVE

CALIBRATION

相关PDF资料 |

PDF描述 |

|---|---|

| M48T59V-70PC1 | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59V-70PC1TR | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59V-70PC6 | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59V-70PC6TR | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59MH | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M48T59V-70PC1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3 V, 64 Kbit (8 Kbit x 8) TIMEKEEPER? SRAM |

| M48T59V-70PC1E | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3 V, 64 Kbit (8 Kbit x 8) TIMEKEEPER? SRAM |

| M48T59V-70PC1F | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.3 V, 64 Kbit (8 Kbit x 8) TIMEKEEPER? SRAM |

| M48T59V-70PC1TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59V-70PC6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM |

发布紧急采购,3分钟左右您将得到回复。