- 您现在的位置:买卖IC网 > PDF目录359066 > M48T59V-70PC6 (意法半导体) 64 Kbit 8Kb x8 TIMEKEEPER SRAM PDF资料下载

参数资料

| 型号: | M48T59V-70PC6 |

| 厂商: | 意法半导体 |

| 英文描述: | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| 中文描述: | 64千位8KB的x8 SRAM的计时器 |

| 文件页数: | 7/21页 |

| 文件大小: | 168K |

| 代理商: | M48T59V-70PC6 |

7/21

M48T59, M48T59Y, M48T59V

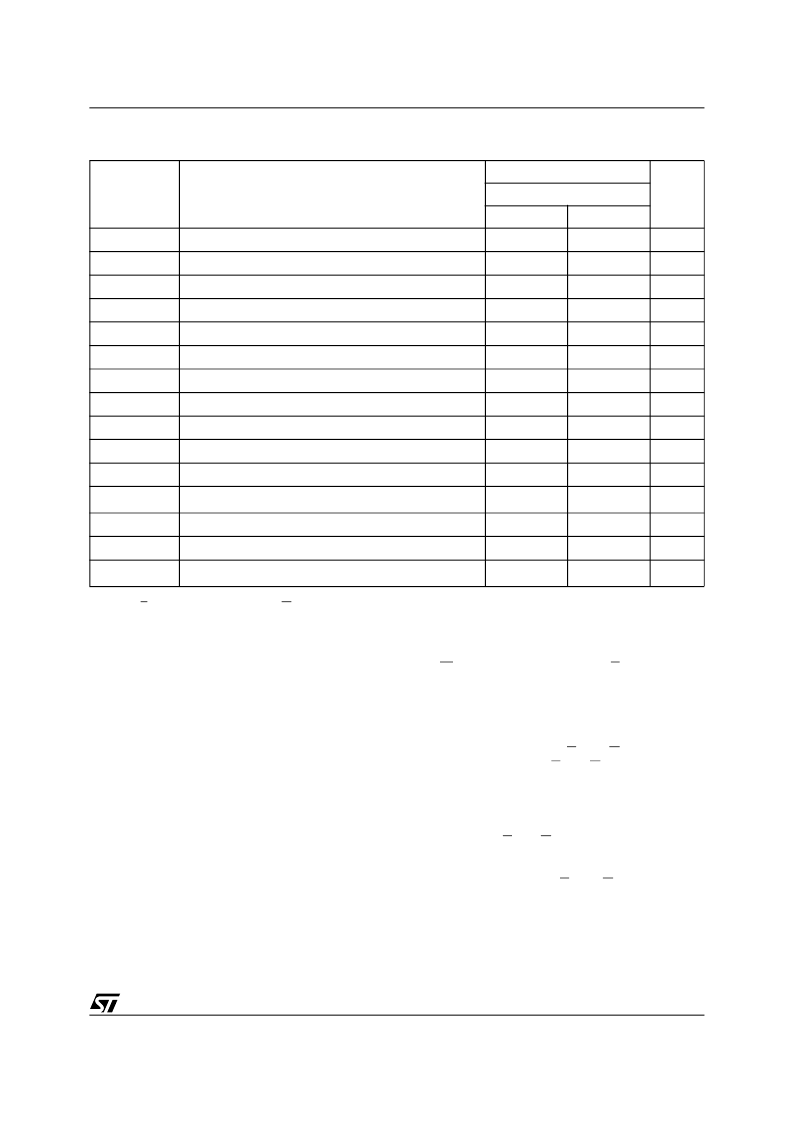

Table 10. Write Mode AC Characteristics

(T

A

= 0 to 70 °C or –40 to 85 °C; V

CC

= 4.75V to 5.5V or 4.5V to 5.5V or 3.0V to 3.6V)

Note: 1. C

L

= 5pF (see Fig 4).

2. If E goes low simultaneously with W going low, the outputs remain in the high impedance state.

Symbol

Parameter

M48T59/M48T59Y/M48T59V

Unit

-70

Min

Max

t

AVAV

Write Cycle Time

70

ns

t

AVWL

Address Valid to Write Enable Low

0

ns

t

AVEL

Address Valid to Chip Enable Low

0

ns

t

WLWH

Write Enable Pulse Width

50

ns

t

ELEH

Chip Enable Low to Chip Enable High

55

ns

t

WHAX

Write Enable High to Address Transition

0

ns

t

EHAX

Chip Enable High to Address Transition

0

ns

t

DVWH

Input Valid to Write Enable High

30

ns

t

DVEH

Input Valid to Chip Enable High

30

ns

t

WHDX

Write Enable High to Input Transition

5

ns

t

EHDX

Chip Enable High to Input Transition

5

ns

t

WLQZ

(1, 2)

Write Enable Low to Output Hi-Z

25

ns

t

AVWH

Address Valid to Write Enable High

60

ns

t

AVE1H

Address Valid to Chip Enable High

60

ns

t

WHQX

(1, 2)

Write Enable High to Output Transition

5

ns

The eight clock bytes are not the actual clock

counters themselves; they are memory locations

consisting of BiPORT read/write memory cells.

The M48T59/59Y/59V includes a clock control cir-

cuit which updates the clock bytes with current in-

formation once per second. The information can

be accessed by the user in the same manner as

any other location in the static memory array.

The M48T59/59Y/59V also has its own Power-fail

Detect circuit. The control circuitry constantly mon-

itors the single 5V supply for an out of tolerance

condition. When V

CC

is out of tolerance, the circuit

write protects the SRAM, providing a high degree

of data security in the midst of unpredictable sys-

tem operation brought on by low V

CC

. As V

CC

falls

below approximately 3V, the control circuitry con-

nects the battery which maintains data and clock

operation until valid power returns.

READ MODE

The M48T59/59Y/59V is in the Read Mode when-

ever W (Write Enable) is high and E (Chip Enable)

is low. The unique address specified by the 13 Ad-

dress Inputs defines which one of the 8,192 bytes

of data is to be accessed. Valid data will be avail-

able at the Data I/O pins within Address Access

time (t

AVQV

) after the last address input signal is

stable, providing that the E and G access times

are also satisfied. If the E and G access times are

not met, valid data will be available after the latter

of the Chip Enable Access time (t

ELQV

) or Output

Enable Access time (t

GLQV

).

The state of the eight three-state Data I/O signals

is controlled by E and G. If the outputs are activat-

ed before t

AVQV

, the data lines will be driven to an

indeterminate state until t

AVQV

. If the Address In-

puts are changed while E and G remain active,

output data will remain valid for Output Data Hold

time (t

AXQX

) but will go indeterminate until the next

Address Access.

相关PDF资料 |

PDF描述 |

|---|---|

| M48T59V-70PC6TR | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59MH | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59SH | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59YPC | 5 PIN DIN CABLE 10 FT |

| M48T59V-70MH1TR | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M48T59V-70PC6TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59VMH | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59VPC | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59VSH | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59Y | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM |

发布紧急采购,3分钟左右您将得到回复。