- 您现在的位置:买卖IC网 > PDF目录359066 > M48T59VMH (意法半导体) 64 Kbit 8Kb x8 TIMEKEEPER SRAM PDF资料下载

参数资料

| 型号: | M48T59VMH |

| 厂商: | 意法半导体 |

| 英文描述: | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| 中文描述: | 64千位8KB的x8 SRAM的计时器 |

| 文件页数: | 9/21页 |

| 文件大小: | 168K |

| 代理商: | M48T59VMH |

9/21

M48T59, M48T59Y, M48T59V

WRITE MODE

The M48T59/59Y/59V is in the Write Mode when-

ever W and E are low. The start of a write is refer-

enced from the latter occurring falling edge of W or

E. A write is terminated by the earlier rising edge

of W or E. The addresses must be held valid

throughout the cycle. E or W must return high for

a minimum of t

EHAX

from Chip Enable or t

WHAX

from Write Enable prior to the initiation of another

read or write cycle. Data-in must be valid t

DVWH

prior to the end of write and remain valid for t

WHDX

afterward. G should be kept high during write cy-

cles to avoid bus contention; although, if the output

bus has been activated by a low on E and G a low

on W will disable the outputs t

WLQZ

after W falls.

DATA RETENTION MODE

With valid V

CC

applied, the M48T59/59Y/59V op-

erates as a conventional BYTEWIDE static RAM.

Should the supply voltage decay, the RAM will au-

tomatically power-fail deselect, write protecting it-

self when V

CC

falls within the V

PFD

(max), V

PFD

(min) window. All outputs become high imped-

ance, and all inputs are treated as "don’t care."

Note:

A power failure during a write cycle may cor-

rupt data at the currently addressed location, but

does not jeopardize the rest of the RAM’s content.

At voltages below V

PFD

(min), the user can be as-

sured the memory will be in a write protected state,

provided the V

CC

fall time is not less than t

F

. The

M48T59/59Y/59V may respond to transient noise

spikes on V

CC

that reach into the deselect window

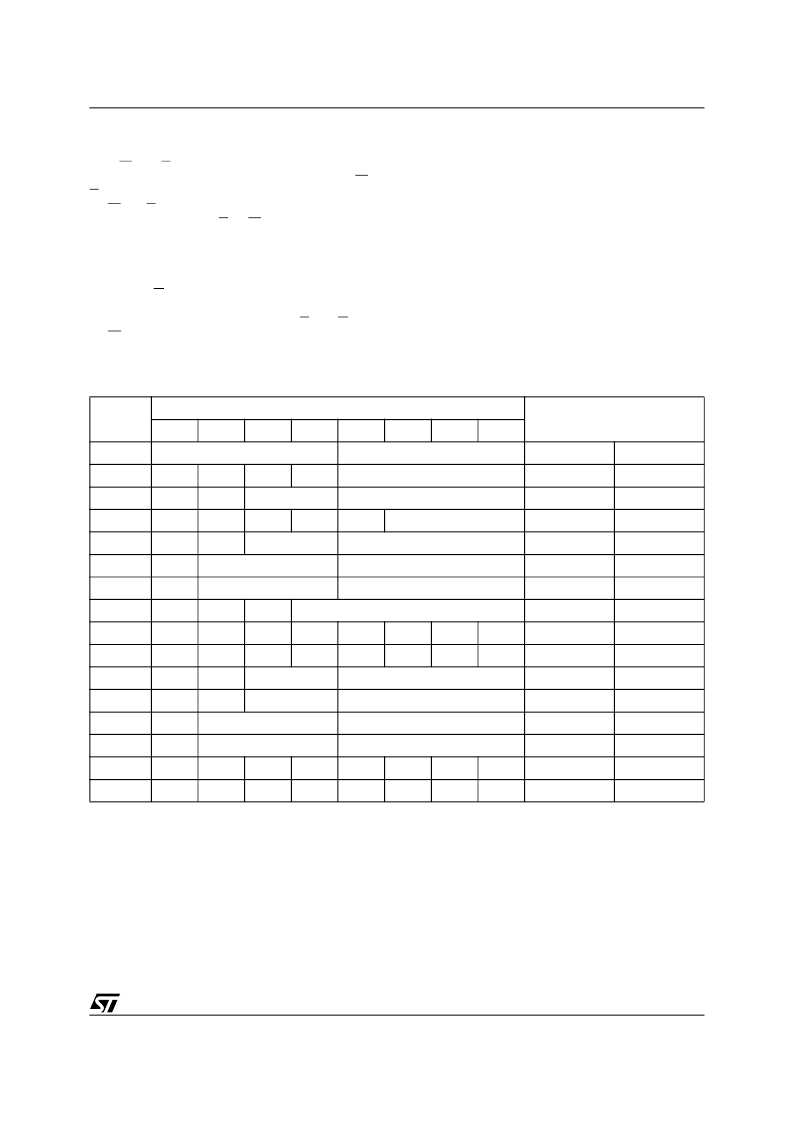

Table 11. Register Map

Address

Data

Function/Range

BCD Format

D7

D6

D5

D4

D3

D2

D1

D0

1FFFh

10 Years

Year

Year

00-99

1FFEh

0

0

0

10 M

Month

Month

01-12

1FFDh

0

0

10 Date

Date

Date

01-31

1FFCh

0

FT

CB

CEB

0

Day

Century/Day

00-01/01-07

1FFBh

0

0

10 Hours

Hours

Hour

00-23

1FFAh

0

10 Minutes

Minutes

Minutes

00-59

1FF9h

ST

10 Seconds

Seconds

Seconds

00-59

1FF8h

W

R

S

Calibration

Control

1FF7h

WDS

BMB4

BMB3

BMB2

BMB1

BMB0

RB1

RB0

Watchdog

1FF6h

AFE

Y

ABE

Y

Y

Y

Y

Y

Interrupts

1FF5h

RPT4

Y

Al. 10 Date

Alarm Date

Alarm Date

01-31

1FF4h

RPT3

Y

Al. 10 Hours

Alarm Hours

Alarm Hours

00-23

1FF3h

RPT2

Alarm 10 Minutes

Alarm Minutes

Alarm Minutes

00-59

1FF2h

RPT1

Alarm 10 Seconds

Alarm Seconds

Alarm Seconds

00-59

1FF1h

Y

Y

Y

Y

Y

Y

Y

Y

Unused

1FF0h

WDF

AF

Z

BL

Z

Z

Z

Z

Flags

Keys:

S = SIGN Bit

FT = FREQUENCY TEST Bit

R = READ Bit

W = WRITE Bit

ST = STOP Bit

0 = Must be set to zero

Y = ’1’ or ’0’

Z = ’0’ and are Read only

AF = Alarm Flag

BL = Battery Low

WDS = Watchdog Steering Bit

BMB0-BMB4 = Watchdog Multiplier Bits

RB0-RB1 = Watchdog Resolution Bits

AFE = Alarm Flag Enable

ABE = Alarm in Battery Back-up Mode Enable

RPT1-RPT4 = Alarm Repeat Mode Bits

WDF = Watchdog Flag

CEB = Century Enable Bit

CB = Century Bit

相关PDF资料 |

PDF描述 |

|---|---|

| M48T59PC | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59V-70MH6TR | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59V-70PC1 | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59V-70PC1TR | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59V-70PC6 | 64 Kbit 8Kb x8 TIMEKEEPER SRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M48T59VPC | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59VSH | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59Y | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:64 Kbit 8Kb x8 TIMEKEEPER SRAM |

| M48T59Y-70MH1 | 功能描述:实时时钟 U 511-M48T59Y-70MH1E RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

| M48T59Y-70MH1E | 功能描述:实时时钟 64K (8Kx8) 70ns RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。