- 您现在的位置:买卖IC网 > PDF目录377832 > M54HC693 (意法半导体) Binary Up/Down Counter/Register(二进制计数器/寄存器) PDF资料下载

参数资料

| 型号: | M54HC693 |

| 厂商: | 意法半导体 |

| 元件分类: | 通用总线功能 |

| 英文描述: | Binary Up/Down Counter/Register(二进制计数器/寄存器) |

| 中文描述: | 二进制加/减计数器/寄存器(二进制计数器/寄存器) |

| 文件页数: | 1/23页 |

| 文件大小: | 433K |

| 代理商: | M54HC693 |

M54/74HC690/691

M54/74HC692/693

March 1993

HC691/693 4 BIT BINARY COUNTER/REGISTER (3-STATE)

.

HIGH SPEED

f

MAX

= 50 MHz (TYP.) at V

CC

= 5 V

.

LOWPOWER DISSIPATION

I

CC

= 4

μ

A(MAX.) at T

A

= 25

°

C

.

HIGH NOISE IMMUNITY

V

NIH

= V

NIL

= 28 % V

CC

(MIN.)

.

OUTPUT DRIVE CAPABILITY

15 LSTTL LOADS (forQ

A

to Q

D

)

10 LSTTL LOADS (forRCO)

.

SYMMETRICAL OUTPUT IMPEDANCE

I

OH

= I

OL

= 6 mA (MIN.) (for Q

A

toQ

D

)

I

OH

= I

OL

= 4 mA (MIN.) (for RCO)

.

BALANCEDPROPAGATION DELAYS

t

PLH

= t

PHL

.

WIDE OPERATING VOLTAGE RANGE

V

CC

(OPR) = 2 V to 6 V

.

PIN ANDFUNCTION COMPATIBLE

WITH LSTTL 54/74LS690/691

HC690/692 DECADE COUNTER/REGISTER (3-STATE)

B1R

(Plastic Package)

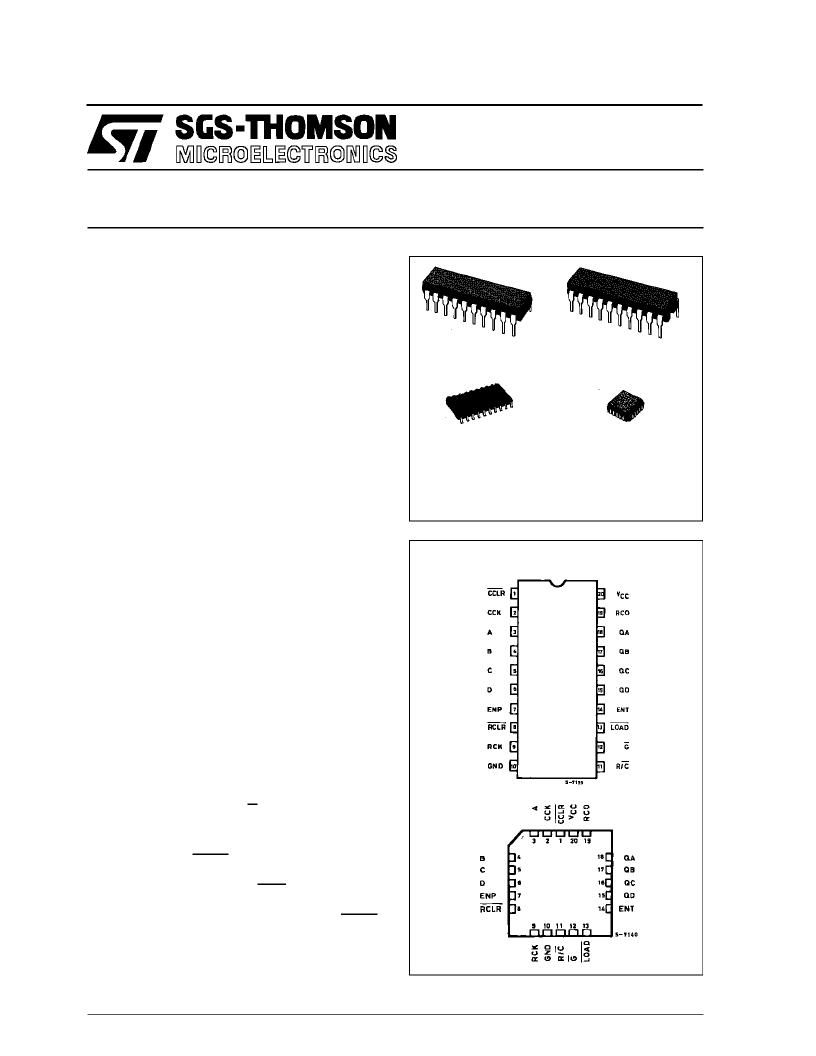

ORDER CODES :

M54HCXXXF1R

M74HCXXXB1R

M74HCXXXM1R

M74HCXXXC1R

F1R

(CeramicPackage)

M1R

(MicroPackage)

C1R

(Chip Carrier)

PIN CONNECTIONS

(top view)

NC =

No Internal

Connection

The HC690/691/692/693 are high speed CMOS

COUNTER/REGISTER fabricated in silicon gate

C

2

MOS technology.

They have the same high speed performance of

LSTTL combined with true CMOS low power con-

sumption.

The internal circuit is composed of 3 stages includ-

ing buffer output, which offers high noise immunity

and stableoutput.Thesedevices incorporate a syn-

chronous counter, four-bit D-type register, and

quadruple two-line to one-line multiplexers with

three-state outputs in a single 20-pin package. The

counter can be programmed from the data inputs

and have enablePandenable Tinputs anda ripple-

carry output for easy expansion.

ter/counter select input, R/C, selects the counter

when low or the register when high for the three-

state outputs, QA, QB, QC, and QD.

If the LOADinput (LOAD)isheld ”L” DATAinput(A-

D) are loaded in to the internal counter at positive

edge of counter clock input (CCK). In the counter

mode, internal counter counts up at the positive of

the counter clock.If thecounter clear input (CCLR)

isheld”L”,theinternalcounteriscleared(synchron-

ously to the counter clock for HC692/HC693, and

asynchronously for HC690/HC691). The internal

The regis-

DESCRIPTION

1/23

相关PDF资料 |

PDF描述 |

|---|---|

| M54HC696 | Decade Up/Down Counter/Register(十进制加/减计数器/寄存器(三态)) |

| M54HC7640 | Octal Bus Transceiver(八总线收发器) |

| M54HC7643 | Octal Bus Transceiver(八总线收发器) |

| M54HC7645 | Octal Bus Transceiver(八总线收发器) |

| M54HC76 | Dual D Type Flip Flop with Preset and Clear(带复位和清除的双D触发器) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M54HC74K | 制造商:STMicroelectronics 功能描述:LOGIC, 5VOLTSFLIP FLOPDUAL D-TYPE FF + PRESET+CLEARFLAT-14 S - Bulk |

| M54HC86K | 制造商:STMicroelectronics 功能描述: |

| M54HCT244K | 制造商:STMicroelectronics 功能描述:BFFR/LINE DRVR OCTAL NON-INV 3-ST CMOS 20PIN FPC - Bulk 制造商:STMicroelectronics 功能描述:LOGIC, 5VOLTSOCTAL BUFFEROCTAL BUS BUFFER, 3-STATE FLAT-20 - Bulk |

| M54HCT244K1 | 制造商:STMicroelectronics 功能描述: |

| M54HCT245K | 制造商:STMicroelectronics 功能描述:LOGIC, 5VOLTSOCTAL BUSOCTAL BUS TRANSCEIVER - 3-STATEFLAT-20 - Bulk |

发布紧急采购,3分钟左右您将得到回复。