- 您现在的位置:买卖IC网 > PDF目录180222 > M5LV-320/184-12HC (LATTICE SEMICONDUCTOR CORP) Fifth Generation MACH Architecture PDF资料下载

参数资料

| 型号: | M5LV-320/184-12HC |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | Fifth Generation MACH Architecture |

| 中文描述: | EE PLD, 12 ns, PQFP240 |

| 封装: | HEAT SINK, PLASTIC, QFP-240 |

| 文件页数: | 17/47页 |

| 文件大小: | 1145K |

| 代理商: | M5LV-320/184-12HC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页

24

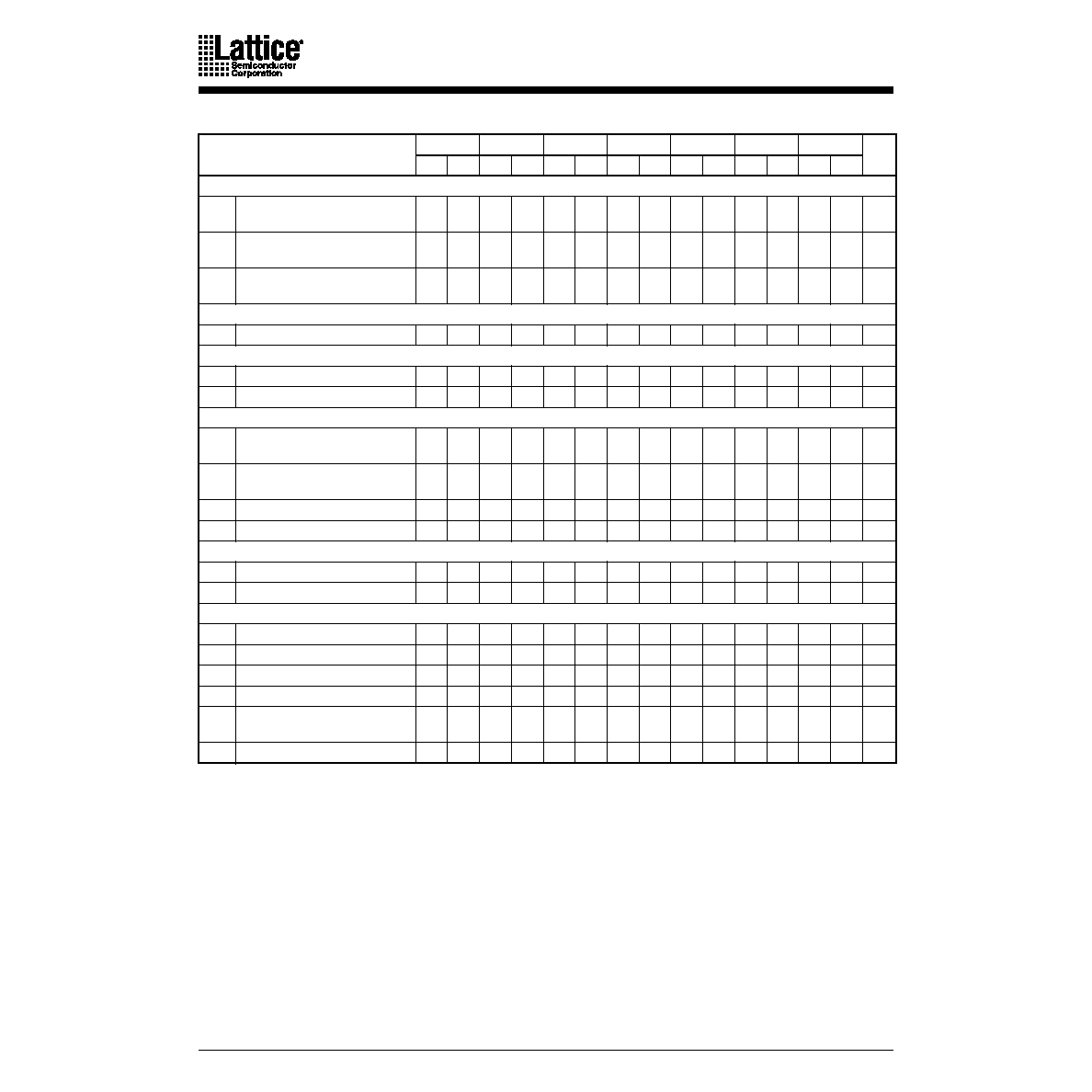

MACH 5 Family

Power Delays:

tPL1

Power level 1 delay (Note 2)

4.0

(5.0)

4.0

(5.0)

4.0

(5.0)

4.0

(5.0)

4.0

(5.0)

4.0

(5.0)

ns

tPL2

Power level 2 delay (Note 2)

6.0

(9.0)

6.0

(9.0)

6.0

(9.0)

6.0

(9.0)

6.0

(9.0)

6.0

(9.0)

ns

tPL3

Power level 3 delay (Note 2)

9.0

(17.5)

9.0

(17.5)

9.0

(17.5)

9.0

(17.5)

9.0

(17.5)

9.0

(17.5)

ns

Additional Cluster Delay:

tPT

Product term cluster delay

0.3

ns

Interconnect Delays:

tBLK

Block interconnect delay

1.5

2.0

ns

tSEG

Segment interconnect delay

4.5

5.0

6.0

ns

Reset and Preset Delays:

tSRi

Asynchronous reset or preset to internal

register output

6.0

8.0

10.0

12.0

14.0

16.0

ns

tSR

Asynchronous reset or preset to register

output

8.0

10.0

12.0

14.0

16.0

18.0

ns

tSRR

Reset and set register recovery time

5.5

7.5

8.0

9.0

10.0

11.0

ns

tSRW

Asynchronous reset or preset width

3.0

4.0

5.0

6.0

7.0

8.0

ns

Clock Enable Delays:

tCES

Clock enable setup time

4.0

5.0

6.0

7.0

8.0

ns

tCEH

Clock enable hold time

3.0

4.0

5.0

6.0

7.0

ns

Width:

tWLS

Global clock width low (Note 3)

2.5

3.0

4.0

5.0

6.0

ns

tWHS

Global clock width high (Note 3)

2.5

3.0

4.0

5.0

6.0

ns

tWLA

Product term clock width low

3.0

4.0

5.0

6.0

7.0

8.0

ns

tWHA

Product term clock width high

3.0

4.0

5.0

6.0

7.0

8.0

ns

tGWA

Gate width low (for low transparent) or

high (for high transparent)

3.0

4.0

5.0

6.0

7.0

8.0

ns

tWIR

Input register clock width low or high

3.0

4.0

5.0

6.0

7.0

8.0

ns

M5(LV) TIMING PARAMETERS OVER OPERATING RANGES1 (CONTINUED)

-5

-6

-7

-10

-12

-15

-20

Unit

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

相关PDF资料 |

PDF描述 |

|---|---|

| M5LV-320/184-12HI | Fifth Generation MACH Architecture |

| M5LV-320/184-15HC | Fifth Generation MACH Architecture |

| M5LV-320/184-15HI | Fifth Generation MACH Architecture |

| M5LV-320/184-20HI | Fifth Generation MACH Architecture |

| M5LV-320/184-6HC | Fifth Generation MACH Architecture |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M5LV-384/120-10YC | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M5LV-384/120-10YI | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M5LV-384/120-12YC | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M5LV-384/120-12YI | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M5LV-384/120-15YC | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。