- 您现在的位置:买卖IC网 > PDF目录180222 > M5LV-320/184-20HI (LATTICE SEMICONDUCTOR CORP) Fifth Generation MACH Architecture PDF资料下载

参数资料

| 型号: | M5LV-320/184-20HI |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | Fifth Generation MACH Architecture |

| 中文描述: | EE PLD, 20 ns, PQFP240 |

| 封装: | HEAT SINK, PLASTIC, QFP-240 |

| 文件页数: | 10/47页 |

| 文件大小: | 1145K |

| 代理商: | M5LV-320/184-20HI |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页

18

MACH 5 Family

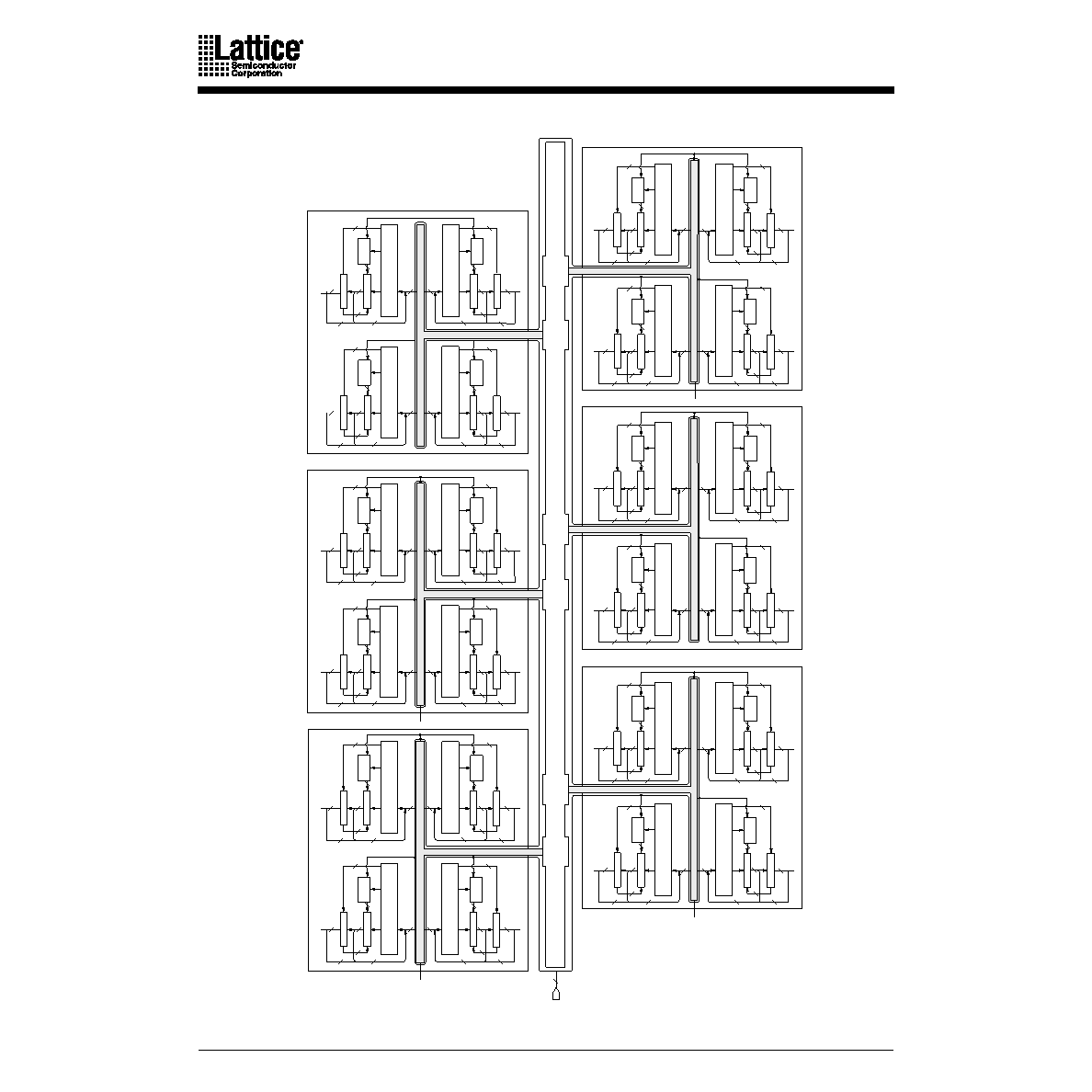

BLOCK DIAGRAM — M5(LV)-384/XXX

Macrocells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Control

Generator

64

PT

2

PT

OE

I/O

Cells

16

32

7

PT

7

2

32

16

Macrocells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Control

Generator

64

PT

2

PT

OE

I/O

Cells

16

32

7

PT

7

2

32

16

Macrocells

Control

Generator

64

PT

2

PT

OE

16

32

7

PT

7

2

32

16

I/O

Cells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Macrocells

Control

Generator

64

PT

2

PT

OE

16

32

7

PT

7

2

32

16

I/O

Cells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Block

A/Macrocells

0-15

Block

D/Macrocells

0-15

Block

B/Macrocells

0-15

Block

C/Macrocells

0-15

Block

Interconnect

Macrocells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Control

Generator

64

PT

2

PT

OE

I/O

Cells

16

32

7

PT

7

2

32

16

Macrocells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Control

Generator

64

PT

2

PT

OE

I/O

Cells

16

32

7

PT

7

2

32

16

Macrocells

Control

Generator

64

PT

2

PT

OE

16

32

7

PT

7

2

32

16

I/O

Cells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Macrocells

Control

Generator

64

PT

2

PT

OE

16

32

7

PT

7

2

32

16

I/O

Cells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Block

A/Macrocells

0-15

Block

D/Macrocells

0-15

Block

B/Macrocells

0-15

Block

C/Macrocells

0-15

Block

Interconnect

Macrocells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Control

Generator

64

PT

2

PT

OE

I/O

Cells

16

32

7

PT

7

2

32

16

Macrocells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Control

Generator

64

PT

2

PT

OE

I/O

Cells

16

32

7

PT

7

2

32

16

Macrocells

Control

Generator

64

PT

2

PT

OE

16

32

7

PT

7

2

32

16

I/O

Cells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Macrocells

Control

Generator

64

PT

2

PT

OE

16

32

7

PT

7

2

32

16

I/O

Cells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Block

A/Macrocells

0-15

Block

D/Macrocells

0-15

Block

B/Macrocells

0-15

Block

C/Macrocells

0-15

Block

Interconnect

Macrocells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Control

Generator

64

PT

2

PT

OE

I/O

Cells

16

32

7

PT

7

2

32

16

Macrocells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Control

Generator

64

PT

2

PT

OE

I/O

Cells

16

32

7

PT

7

2

32

16

Macrocells

Control

Generator

64

PT

2

PT

OE

16

32

7

PT

7

2

32

16

I/O

Cells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Macrocells

Control

Generator

64

PT

2

PT

OE

16

32

7

PT

7

2

32

16

I/O

Cells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Block

A/Macrocells

0-15

Block

D/Macrocells

0-15

Block

B/Macrocells

0-15

Block

C/Macrocells

0-15

Block

Interconnect

S

E

G

M

E

N

T

CLK0

CLK1

CLK2

CLK3

4

SEGMENT

0

SEGMENT

5

SEGMENT

2

SEGMENT

1

I 0

I 1

I 2

Macrocells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Control

Generator

64

PT

2

PT

OE

I/O

Cells

16

32

7

PT

7

2

32

16

Macrocells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Control

Generator

64

PT

2

PT

OE

I/O

Cells

16

32

7

PT

7

2

32

16

Macrocells

Control

Generator

64

PT

2

PT

OE

16

32

7

PT

7

2

32

16

I/O

Cells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Macrocells

Control

Generator

64

PT

2

PT

OE

16

32

7

PT

7

2

32

16

I/O

Cells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Block

A/Macrocells

0-15

Block

D/Macrocells

0-15

Block

B/Macrocells

0-15

Block

C/Macrocells

0-15

Block

Interconnect

IN

T

E

R

C

O

N

E

C

T

SEGMENT

3

Macrocells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Control

Generator

64

PT

2

PT

OE

I/O

Cells

16

32

7

PT

7

2

32

16

Macrocells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Control

Generator

64

PT

2

PT

OE

I/O

Cells

16

32

7

PT

7

2

32

16

Macrocells

Control

Generator

64

PT

2

PT

OE

16

32

7

PT

7

2

32

16

I/O

Cells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Macrocells

Control

Generator

64

PT

2

PT

OE

16

32

7

PT

7

2

32

16

I/O

Cells

64

x

73

AND

Logic

Array

and

Logic

Allocator

Block

A/Macrocells

0-15

Block

D/Macrocells

0-15

Block

B/Macrocells

0-15

Block

C/Macrocells

0-15

Block

Interconnect

I 3

SEGMENT

4

20446G-011

相关PDF资料 |

PDF描述 |

|---|---|

| M5LV-320/184-6HC | Fifth Generation MACH Architecture |

| M5LV-320/184-7HC | Fifth Generation MACH Architecture |

| M5LV-320/192-10AC | Fifth Generation MACH Architecture |

| M5LV-320/192-10AI | Fifth Generation MACH Architecture |

| M5LV-320/192-12AC | Fifth Generation MACH Architecture |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M5LV-384/120-10YC | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M5LV-384/120-10YI | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M5LV-384/120-12YC | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M5LV-384/120-12YI | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| M5LV-384/120-15YC | 功能描述:CPLD - 复杂可编程逻辑器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。