- 您现在的位置:买卖IC网 > PDF目录370970 > M5M465805BTP-6 (Mitsubishi Electric Corporation) EDO MODE 67108864-BIT (16777216-WORD BY 4-BIT) DYNAMIC RAM PDF资料下载

参数资料

| 型号: | M5M465805BTP-6 |

| 厂商: | Mitsubishi Electric Corporation |

| 英文描述: | EDO MODE 67108864-BIT (16777216-WORD BY 4-BIT) DYNAMIC RAM |

| 中文描述: | 江户模式67108864位(16777216 - Word的4位)动态随机存储器 |

| 文件页数: | 12/39页 |

| 文件大小: | 403K |

| 代理商: | M5M465805BTP-6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页

MITSUBISHI

ELECTRIC

Jun. 1999

EDO MODE 67108864-BIT (16777216-WORD BY 4-BIT) DYNAMIC RAM

EDO MODE 67108864-BIT (8388608-WORD BY 8-BIT) DYNAMIC RAM

EDO MODE 67108864-BIT (4194304-WORD BY 16-BIT) DYNAMIC RAM

MITSUBISHI LSIs

(Rev. 1.1)

M5M467405/465405BJ,BTP -5,-6,-5S,-6S

M5M467805/465805BJ,BTP -5,-6,-5S,-6S

M5M465165BJ,BTP -5,-6,-5S,-6S

12

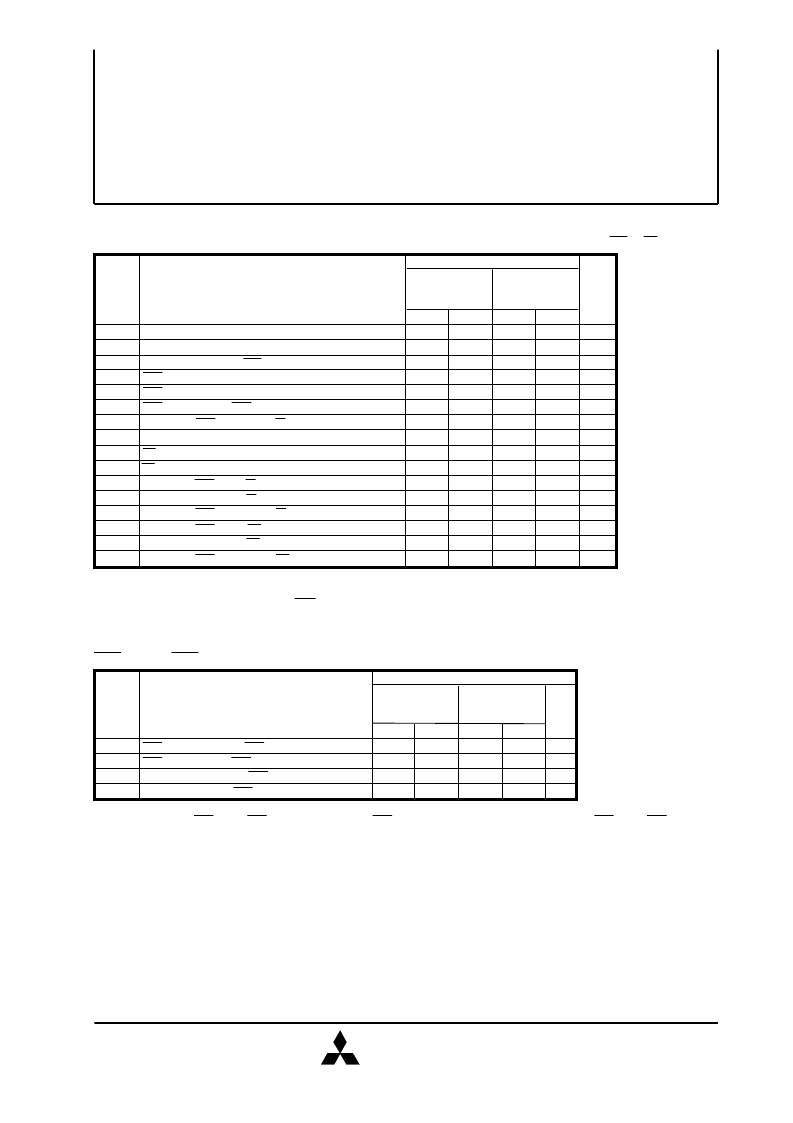

CAS before RAS Refresh Cycle

(Note 28)

Note 28: Eight or more CAS before RAS cycles instead of eight RAS cycles are necessary for proper operation of CAS before RAS refresh mode.

EDO Mode Cycle (Read, Early Write, Read-Write, Read-Modify-Write Cycle,

Read Write Mix Cycle, Hi-Z control by OE or W)

(Note 25)

Parameter

Symbol

Limits

Unit

Parameter

Symbol

Limits

Unit

CAS setup time before RAS low

CAS hold time after RAS low

Read setup time before RAS low

t

CSR

t

CHR

t

RSR

t

RHR

Read hold time after RAS low

5

10

10

10

5

10

10

10

ns

ns

ns

ns

Min

Max

Min

Max

EDO mode read/write cycle time

EDO Mode read write / read modify write cycle time

RAS low pulse width for read write cycle

CAS high pulse width

RAS hold time after CAS precharge

Delay time, CAS precharge to W low

Hold time to maintain the data Hi-Z until CAS access

t

HPC

t

HPRWC

t

RAS

t

CP

t

CPRH

t

CPWD

t

CHOL

(Note26)

(Note27)

28

43

7

7

20

55

8

(Note24)

100000

13

33

50

7

7

25

66

10

100000

16

t

OEPE

t

WPE

t

HCWD

OE Pulse Width (Hi-Z control)

W Pulse Width (Hi-Z control)

Delay time, CAS low to W low after read

Delay time, Address to W low after read

Delay time, CAS precharge to W low after read

Delay time, CAS low to OE high after read

Delay time, Address to OE high after read

7

28

7

32

ns

ns

ns

ns

ns

ns

ns

ns

Min

Max

Min

Max

ns

ns

5

5

t

DOH

Output hold time from CAS low

Delay time, CAS precharge to OE high after read

t

HAWD

t

HPWD

t

HCOD

t

HAOD

t

HPOD

40

43

13

47

50

15

25

28

30

33

ns

ns

ns

ns

ns

ns

65

77

Note 25: All previously specified timing requirements and switching characteristics are applicable to their respective EDO mode cycle.

26: t

RAS(min)

is specified as two cycles of CAS input are performed.

27: t

CP(max)

is specified as a reference point only. If t

CP

t

CP(max) ,

access time is controlled exclusively by tCAC.

M5M46X405B-5,5S

M5M46X805B-5,5S

M5M465165B-5,5S

M5M46X405B-6,6S

M5M46X805B-6,6S

M5M465165B-6,6S

M5M46X405B-5,5S

M5M46X805B-5,5S

M5M465165B-5,5S

M5M46X405B-6,6S

M5M46X805B-6,6S

M5M465165B-6,6S

相关PDF资料 |

PDF描述 |

|---|---|

| M5M465805BTP-6S | EDO MODE 67108864-BIT (16777216-WORD BY 4-BIT) DYNAMIC RAM |

| M5M467805BJ | EDO MODE 67108864-BIT (16777216-WORD BY 4-BIT) DYNAMIC RAM |

| M5M467805BTP-5 | EDO MODE 67108864-BIT (16777216-WORD BY 4-BIT) DYNAMIC RAM |

| M5M467805BTP-5S | EDO MODE 67108864-BIT (16777216-WORD BY 4-BIT) DYNAMIC RAM |

| M5M467805BTP-6 | EDO MODE 67108864-BIT (16777216-WORD BY 4-BIT) DYNAMIC RAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M5M465805BTP-6S | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:EDO MODE 67108864-BIT (16777216-WORD BY 4-BIT) DYNAMIC RAM |

| M5M465805DJ | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:EDO MODE 67108864-BIT (16777216-WORD BY 4-BIT) DYNAMIC RAM |

| M5M465805DTP-5 | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:EDO MODE 67108864-BIT (16777216-WORD BY 4-BIT) DYNAMIC RAM |

| M5M465805DTP-5S | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:EDO MODE 67108864-BIT (16777216-WORD BY 4-BIT) DYNAMIC RAM |

| M5M465805DTP-6 | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:EDO MODE 67108864-BIT (16777216-WORD BY 4-BIT) DYNAMIC RAM |

发布紧急采购,3分钟左右您将得到回复。