- 您现在的位置:买卖IC网 > PDF目录370982 > M5M5V208KR-10LL-W (Mitsubishi Electric Corporation) 2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM PDF资料下载

参数资料

| 型号: | M5M5V208KR-10LL-W |

| 厂商: | Mitsubishi Electric Corporation |

| 英文描述: | 2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM |

| 中文描述: | 2097152位(262144 - Word的8位)的CMOS静态RAM |

| 文件页数: | 2/7页 |

| 文件大小: | 88K |

| 代理商: | M5M5V208KR-10LL-W |

MITSUBISHI LSIs

2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM

MITSUBISHI

ELECTRIC

M5M5V208FP,VP,RV,KV,KR

-70L-W , -85L -W, -10L-W , -12L-W ,

-70LL-W, -85LL-W, -10LL-W, -12LL-W

'97.3.21

FUNCTION

The operation mode of the M5M5V208 is determined by a

combination of the device control inputs S

1

, S

2

, W and OE.

Each mode is summarized in the function table.

A write cycle is executed whenever the low level W

overlaps with the low level S

1

and the high level S

2

. The

address must be set up before the write cycle and must be

stable during the entire cycle. The data is latched into a cell

on the trailing edge of W, S

1

or S

2

, whichever occurs first,

requiring the set-up and hold time relative to these edge to

be maintained. The output enable OE directly controls the

output stage. Setting the OE at a high level,the output stage

is in a high-impedance state, and the data bus contention

problem in the write cycle is eliminated.

FUNCTION TABLE

DQ

1

DQ

2

DQ

3

DQ

4

DQ

5

DQ

6

DQ

7

DQ

8

V

CC

(3V)

GND

(0V)

W

S

1

S

2

OE

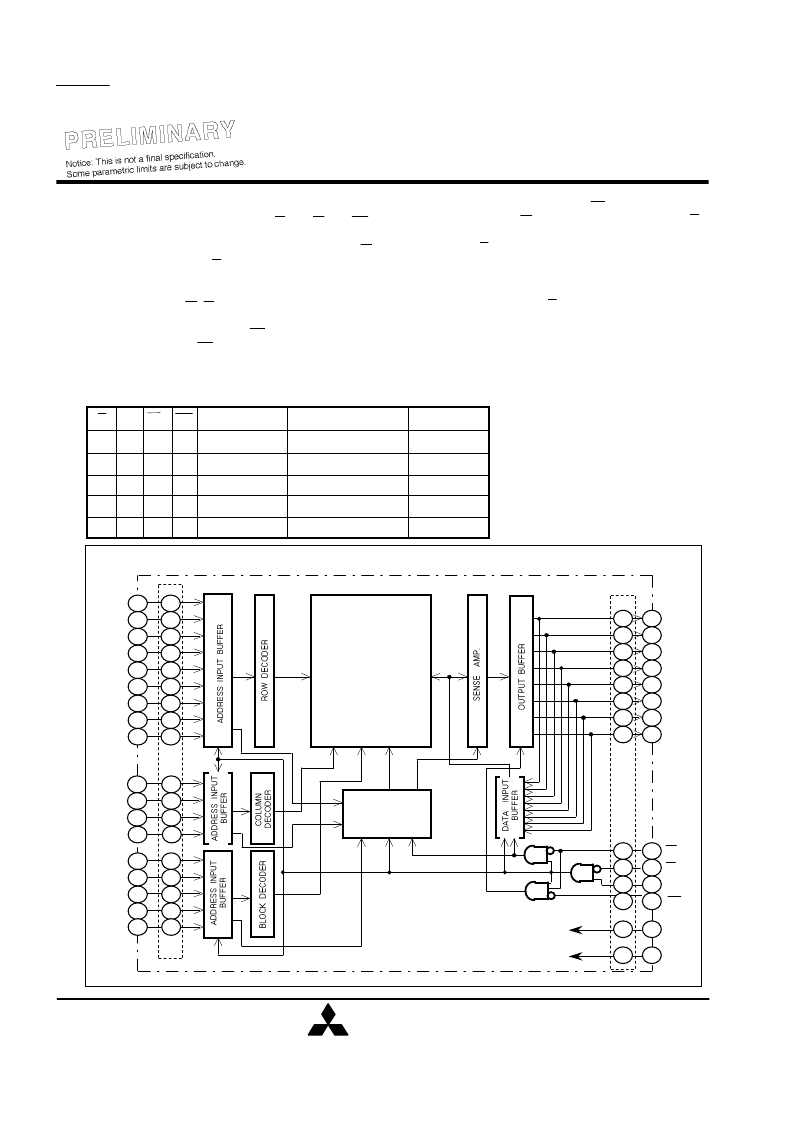

BLOCK DIAGRAM

24

13

14

15

17

32

16

22

18

19

20

21

29

262144 WORDS

X 8 BITS

512 ROWS

X 128 COLUMNS

X 32 BLOCKS

CLOCK

GENERATOR

8

A

4

A

5

A

6

A

7

A

12

A

14

A

16

A

17

A

15

7

6

5

4

3

2

1

31

12

A

0

A

1

A

2

A

3

11

10

23

A

10

A

11

A

9

A

8

A

13

25

26

27

28

A read cycle is executed by setting W at a high level and

OE at a low level while S

1

and S

2

are in an active state (S

1

= L ,S

2

= H).

When setting S

1

at a high level or S

2

at a low level, the

chips are in a non-selectable mode in which both reading

and writing are disabled. In this mode, the output stage is in

a high-impedance state, allowing OR-tie with other chips

and memory expansion by S

1

or S

2

. The power supply

current is reduced as low as the stand-by current which is

specified as Icc3 or Icc4, and the memory data can be held

at +2V power supply, enabling battery back-up operation

during power failure or power-down operation in the non-

selected mode.

Mode

DQ

Icc

S

1

W

OE

Non selection

Write

Read

High-impedance

Standby

Active

Active

Active

High-impedance

D

IN

D

OUT

H

X

X

L

L

L

L

H

H

X

L

H

S

2

L

X

H

X

H

H

X

X

Non selection

High-impedance

Standby

9

30

31

1

2

3

4

20

19

18

17

16

15

14

13

12

11

10

9

7

32

8

24

30

5

6

21

22

23

25

26

27

28

29

*

*

*Pin numbers inside dotted line show those of TSOP.

2

相关PDF资料 |

PDF描述 |

|---|---|

| M5M5V208KR-12LL-W | 2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5V208KR-70L-W | 2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5V208KR-70LL-W | 2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5V208KV-10L-W | 2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5V208KV-10LL-W | 2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M5M5V208KR-10L-W | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5V208KR-12L | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5V208KR-12LL | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5V208KR-12LL-W | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5V208KR-12L-W | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:2097152-BIT (262144-WORD BY 8-BIT) CMOS STATIC RAM |

发布紧急采购,3分钟左右您将得到回复。