- 您现在的位置:买卖IC网 > PDF目录45052 > M8813F3W-15T1 (STMICROELECTRONICS) 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 PDF资料下载

参数资料

| 型号: | M8813F3W-15T1 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 |

| 封装: | PLASTIC, QFP-52 |

| 文件页数: | 14/85页 |

| 文件大小: | 601K |

| 代理商: | M8813F3W-15T1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页当前第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页

21/85

M88 FAMILY

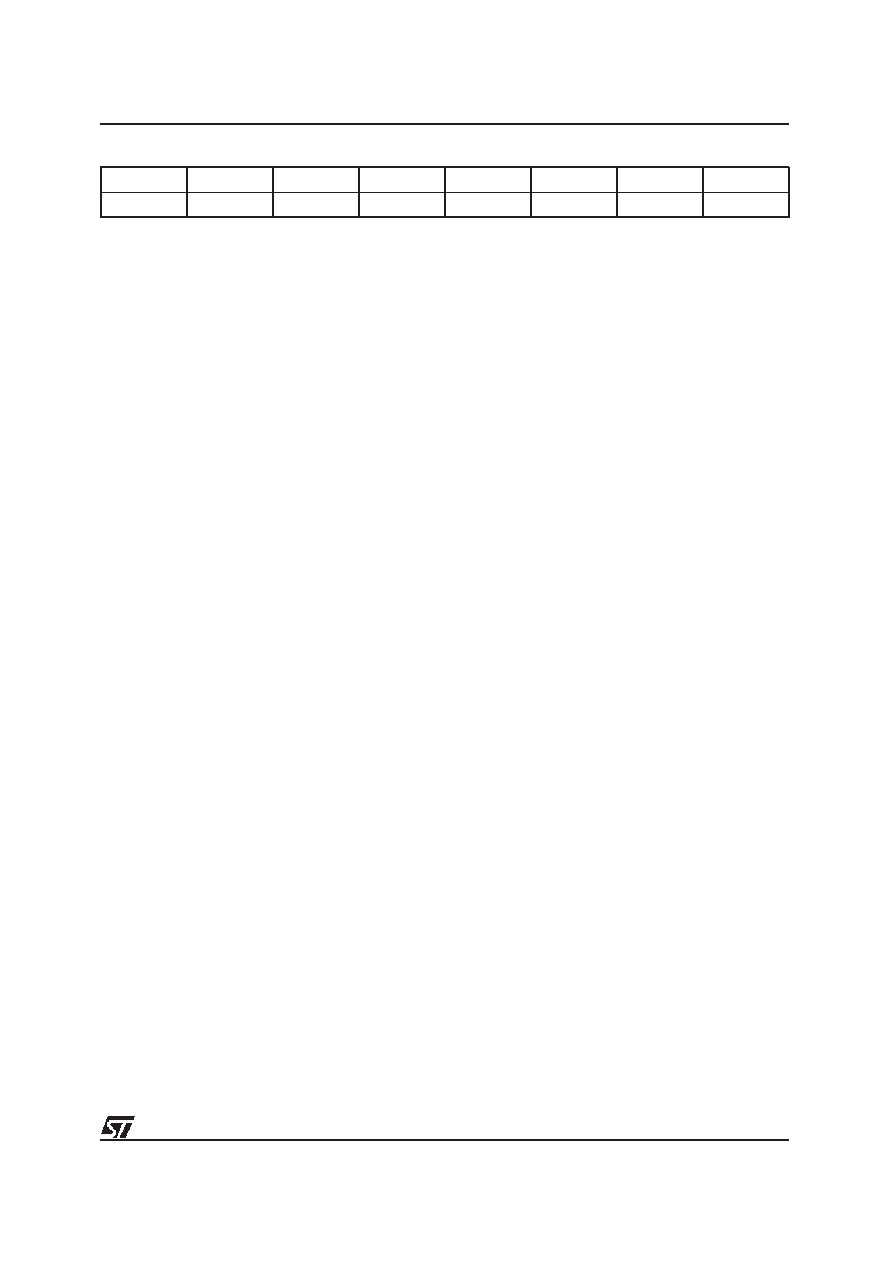

Table 14. Sector Protection/Security Bit Definition – PSD/EE Protection Register

Note: 1. Bit Definitions:

Sec<i>_Prot 1 = EEPROM or Flash Boot Sector <i> is write protected.

Sec<i>_Prot 0 = EEPROM or Flash Boot Sector <i> is not write protected.

Security_Bit 0 = Security Bit in device has not been set.

1 = Security Bit in device has been set.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Security_Bit

not used

Sec3_Prot

Sec2_Prot

Sec1_Prot

Sec0_Prot

EEPROM sectors can be unprotected to allow

updating of their contents using the JTAG Port or

a Device Programmer. The microcontroller can

read (but cannot change) the sector protection

bits.

Any attempt to program or erase a protected Flash

or EEPROM sector will be ignored by the device.

The Verify operation will result in a read of the

protected data. This allows a guarantee of the

retention of the Protection status.

The sector protection status can be read by the

MCU through the Flash protection and PSD/EE

protection registers (CSIOP). See Table 13 and

Table 14.

Reset Instruction

The Reset instruction resets the internal memory

logic state machine in a few milliseconds. Reset is

an instruction of either one write operation or three

write operations (refer to Table 11).

SRAM

The SRAM is a 16 Kbit (2K x 8) memory. The

SRAM is enabled when RS0—the SRAM chip

select output from the DPLD—is high. RS0 can

contain up to two product terms, allowing flexible

memory mapping.

The SRAM can be backed up using an external

battery. The external battery should be connected

to the VSTBY pin (PC2). If you have an external

battery connected to the M8813Fxx FLASH+PSD,

the contents of the SRAM will be retained in the

event of a power loss. The contents of the SRAM

will be retained so long as the battery voltage

remains at 2V or greater. If the supply voltage falls

below the battery voltage, an internal power

switch-over to the battery occurs.

Pin PC4 can be configured as an output that

indicates when power is being drawn from the

external battery. This VBATON signal will be high

with the supply voltage falls below the battery

voltage and the battery on PC2 is supplying power

to the internal SRAM.

The chip select signal (RS0) for the SRAM, VSTBY,

and VBATON are all configured using PSDsoft

Configuration.

Memory Select Signals

The main Flash (FSi), optional EEPROM or Flash

Boot (EESi/CSBOOTi), and SRAM (RS0) memory

select signals are all outputs of the DPLD. They

are setup by writing equations for them in

PSDabel.

The

following rules apply

to

the

equations for the internal chip select signals:

1. Flash memory and EEPROM or Flash Boot

memory sector select signals must not be larger

than the physical sector size.

2. Any main Flash memory sector must not be

mapped in the same memory space as another

Flash sector.

3. An EEPROM/Flash Boot memory sector must

not be mapped in the same memory space as

another EEPROM/Flash Boot sector.

4. SRAM, I/O, and Peripheral I/O spaces must not

overlap.

5. An EEPROM/Flash Boot memory sector may

overlap a main Flash memory sector. In case of

overlap, priority will be given to the EEPROM/

Flash Boot sector.

6. SRAM, I/O, and Peripheral I/O spaces may

overlap any other memory sector. Priority will be

given to the SRAM, I/O, or Peripheral I/O.

Example

FS0 is valid when the address is in the range of

8000h to BFFFh, EES0 is valid from 8000h to

9FFFh, and RS0 is valid from 8000h to 87FFh.

Any address in the range of RS0 will always

access the SRAM. Any address in the range of

EES0 greater than 87FFh (and less than 9FFFh)

will automatically address EEPROM memory

segment 0. Any address greater than 9FFFh will

access the Flash memory segment 0. You can see

that half of the Flash memory segment 0 and one-

fourth of EEPROM segment 0 can not be

accessed in this example. Also note that an

equation that defined FS1 to anywhere in the

range of 8000h to BFFFh would not be valid.

Figure 9 shows the priority levels for all memory

components. Any component on a higher level can

overlap and has priority over any component on a

lower level. Components on the same level must

not overlap. Level one has the highest priority and

level 3 has the lowest.

相关PDF资料 |

PDF描述 |

|---|---|

| M8803F2Y-90T1 | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 |

| M8803F3Y-90T1 | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 |

| M8803F2Y-90T1T | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 |

| M8803F3W-15K1 | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQCC52 |

| M8803F2W-15T1 | 1M X 1 FLASH, 27 I/O, PIA-GENERAL PURPOSE, PQFP52 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M88141W-15K1T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:In-System Programmable ISP Multiple-Memory and Logic FLASHPSD Systems with CPLD for MCUs |

| M88141W-15K6T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:In-System Programmable ISP Multiple-Memory and Logic FLASHPSD Systems with CPLD for MCUs |

| M88141W-15T1T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:In-System Programmable ISP Multiple-Memory and Logic FLASHPSD Systems with CPLD for MCUs |

| M88141W-15T6T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:In-System Programmable ISP Multiple-Memory and Logic FLASHPSD Systems with CPLD for MCUs |

| M88141W-90K1T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:In-System Programmable ISP Multiple-Memory and Logic FLASHPSD Systems with CPLD for MCUs |

发布紧急采购,3分钟左右您将得到回复。