- 您现在的位置:买卖IC网 > PDF目录132964 > M928-02-300.XXXX 300 MHz, OTHER CLOCK GENERATOR, CQCC36 PDF资料下载

参数资料

| 型号: | M928-02-300.XXXX |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 300 MHz, OTHER CLOCK GENERATOR, CQCC36 |

| 封装: | 9 X 9 MM, SMT-36 |

| 文件页数: | 3/6页 |

| 文件大小: | 261K |

| 代理商: | M928-02-300.XXXX |

M928-02 Datasheet Rev 0.3

3 of 6

Revision 013003

Integ r ated Circuit Systems , Inc. ● Comm unications Modules ● www.i cst. com ● tel (508) 852-5400

M928-02

VCSO BASED CLOCK GENERATOR

Preliminar y In f o r m atio n

FUNCTIONAL DESCRIPTION

The M928-02 is a PLL (Phase Locked Loop) based

clock generator that generates output clocks

synchronized to an input reference clock.

The M928-02 combines the flexibility of a VCSO

(Voltage Controlled SAW Oscillator) with the stability of

a crystal oscillator.

Input Reference

The 19.44MHz input reference can either be an external,

discrete crystal device or a stable external clock source

such as a packaged crystal oscillator:

If an external crystal is used with the on-chip crystal

oscillator circuit (XTAL OSC), the external crystal

should be a parallel-resonant, fundamental mode

crystal. Apply it to the XTAL_1 / REF_IN and XTAL_2 input

pins. External crystal load capacitors are also

required.

If an external LVCMOS/LVTTL clock source is used,

apply it to the XTAL_1 / REF_IN input pin.

In either case, the reference clock is supplied directly to

the phase detector of the PLL.

The PLL

The PLL (Phase Locked Loop) includes the phase

detector, the VCSO, and a feedback divider (labeled

“M Divider”).

The feedback divider is a digital circuit that divides the

VCSO output frequency by a numerical value “M” in

order to match the input reference frequency.

By controlling the frequency and phase of the VCSO,

the phase detector precisely locks the frequency and

phase of the feedback divider output to that of the input

reference. This creates an output frequency that is a

multiple of the reference frequency (which is output

from the VCSO).

The relationship between the VCSO output frequency,

the M Divider, and the input reference frequency is

defined as follows:

For the M928-02-622.0800 (see “Ordering Information” on pg. 6):

VCSO output frequency = 622.08MHz

M = 32

Input reference frequency = 19.44MHz

Therefore, for the M928-02-622.0800:

622.08

MHz = 32

19.44

MHz

The VCSO center output frequency of 622.08MHz

enables the product of

to fall within the lock range of the VCSO.

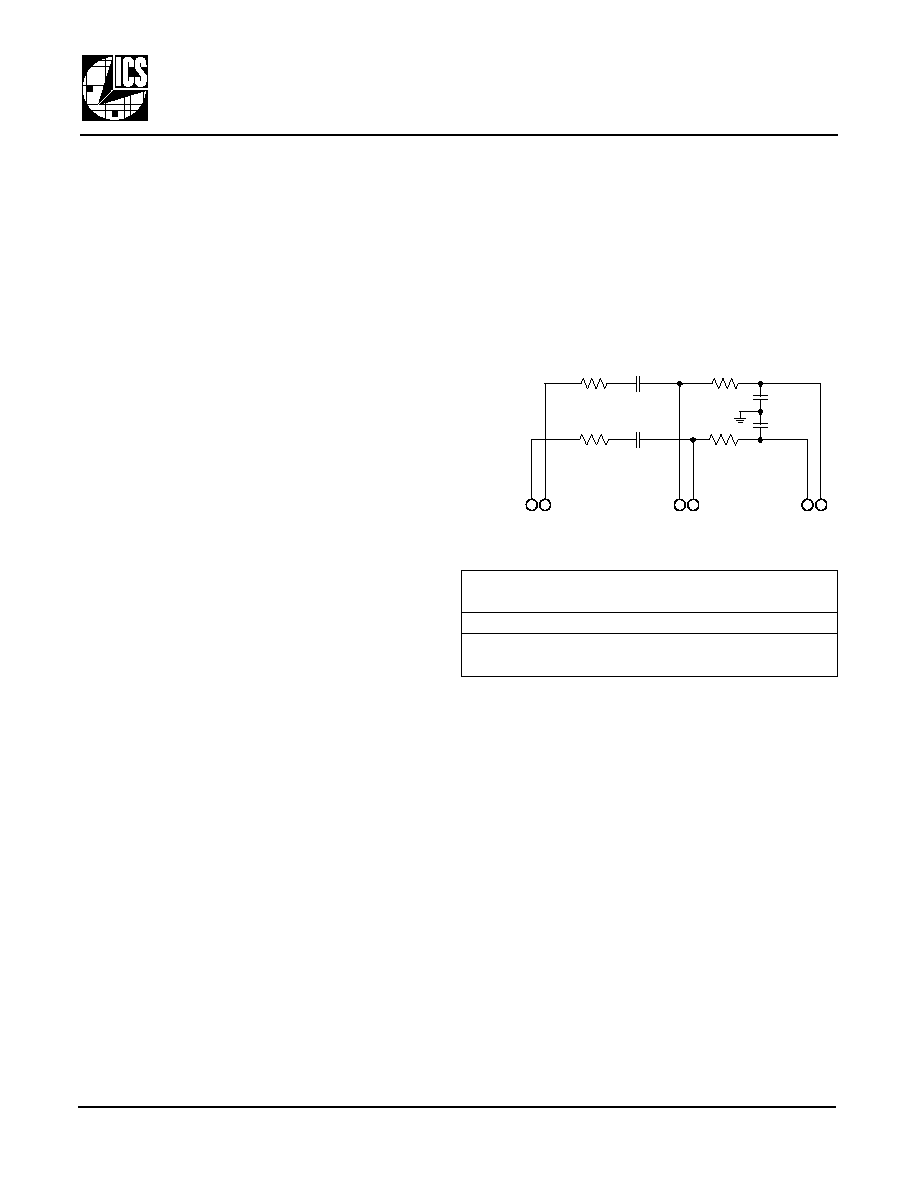

External Loop Filter

To provide stable PLL operation, and thereby a low jitter

output clock, the M928-02 requires the use of an

external loop filter. This is provided via the provided

filter pins (see Figure 4).

Due to the differential signal path design, the

implementation requires two identical complementary

RC filters as shown here.

Figure 4: External Loop Filter

Fvcso

M

Fxtal

×

=

×

External Loop Filter Component Values

PLL

Bandwidth

Damping

Factor

R loop

C loop R post

C post

395

Hz

2.0

1.5

k

4.70F 20k 3300pF

1.2

kHz

2.9

4.7

k

1.00F 20k 1000pF

10

kHz 1

Note 1: Recommended for most applications

2.4

39.0

k

0.01F 20k

240

pF

M

input crystal frequency

×

C

POST

C

POST

VC

nVC

R

POST

nOP_OUT

OP_OUT

R

POST

R

LOOP

R

LOOP

C

LOOP

C

LOOP

OP_IN

nOP_IN

7

相关PDF资料 |

PDF描述 |

|---|---|

| M34551M4-XXXFP | 4-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP48 |

| M37272M8-XXXSP | 8-BIT, MROM, 8.1 MHz, MICROCONTROLLER, PDIP42 |

| M37280MKH-XXXSP | 8-BIT, MROM, 8.1 MHz, MICROCONTROLLER, PDIP64 |

| MSP430F5502IRGZ | 16-BIT, FLASH, 25 MHz, RISC MICROCONTROLLER, PQCC48 |

| MPC9299FN | 400 MHz, OTHER CLOCK GENERATOR, PQCC28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M928-BBCA | 制造商:SECO 功能描述:QUADMO747-X/IMX6Q, 1GB RAM, 4 GB EMMC-ENGINEERING SAMPLE-AVA - Bulk |

| M928-BCCA | 制造商:SECO 功能描述:QUADMO747-X/IMX6Q, 2GB RAM, 4 GB EMMC-ENGINEERING SAMPLE-AVA - Bulk |

| M928-BFDA | 制造商:SECO 功能描述:QUADMO747-X/IMX6Q, 2GB RAM, 8 GB EMMC-ENGINEERING SAMPLE-AVA - Bulk |

| M928-BGCA | 制造商:SECO 功能描述:QUADMO747-X/IMX6Q, 4GB RAM, 4GB EMMC-ENGINEERING SAMPLE-AVAI - Bulk |

| M928-BGDA | 制造商:SECO 功能描述:QUADMO747-X/IMX6Q, 4GB RAM, 8GB EMMC-ENGINEERING SAMPLE-AVAI - Bulk |

发布紧急采购,3分钟左右您将得到回复。