- 您现在的位置:买卖IC网 > PDF目录365230 > MACH211SP-20 (Advanced Micro Devices, Inc.) High-Density EE CMOS Programmable Logic PDF资料下载

参数资料

| 型号: | MACH211SP-20 |

| 厂商: | Advanced Micro Devices, Inc. |

| 英文描述: | High-Density EE CMOS Programmable Logic |

| 中文描述: | 高密度电子工程CMOS可编程逻辑 |

| 文件页数: | 7/37页 |

| 文件大小: | 251K |

| 代理商: | MACH211SP-20 |

第1页第2页第3页第4页第5页第6页当前第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页

MACH211SP-7/10/12/15/20

7

FUNCTIONAL DESCRIPTION

The MACH211SP consists of four PAL blocks con-

nected by a switch matrix. There are 32 I/O pins feeding

the switch matrix. These signals are distributed to the

four PAL blocks for efficient design implementation.

There are two clock pins that can also be used as ded-

icated inputs.

The PAL Blocks

Each PAL block in the MACH211SP (Figure 1) contains

a 64-product-term logic array, a logic allocator, 8 output

macrocells, 8 buried macrocells, and 8 I/O cells. The

switch matrix feeds each PAL block with 26 inputs. This

makes the PAL block look effectively like an indepen-

dent “PAL26V16” with 8 buried macrocells.

In addition to the logic product terms, two output enable

product terms, an asynchronous reset product term,

and an asynchronous preset product term are pro-

vided. One of the two output enable product terms can

be chosen within each I/O cell in the PAL block. All

flip-flops within the PAL block are initialized together.

The Switch Matrix

The MACH211SP switch matrix is fed by the inputs and

feedback signals from the PAL blocks. Each PAL block

provides 16 internal feedback signals and 8 I/O feed-

back signals. The switch matrix distributes these sig-

nals back to the PAL blocks in an efficient manner that

also provides for high performance. The design soft-

ware automatically configures the switch matrix when

fitting a design into the device.

The Product-term Array

The MACH211SP product-term array consists of 64

product terms for logic use, and 4 special-purpose

product terms. Two of the special-purpose product

terms provide programmable output enable; one pro-

vides asynchronous reset, and one provides asynchro-

nous preset.

The Logic Allocator

The logic allocator in the MACH211SP takes the 64

logic product terms and allocates them to the 16

macrocells as needed. Each macrocell can be driven

by up to 16 product terms. The design software auto-

matically configures the logic allocator when fitting the

design into the device.

Table 1 illustrates which product term clusters are avail-

able to each macrocell within a PAL block. Refer to

Figure 1 for cluster and macrocell numbers.

The Macrocell

The MACH211SP has two types of macrocell: output

and buried. The output macrocells can be configured

as either registered, latched, or combinatorial, with pro-

grammable polarity. The macrocell provides internal

feedback whether configured with or without the

flip-flop. The registers can be configured as D-type or

T-type, allowing for product-term optimization.

The flip-flops can individually select one of two clock/

gate pins, which are also available as data inputs. The

registers are clocked on the LOW-to-HIGH transition of

the clock signal. The latch holds its data when the gate

input is HIGH, and is transparent when the gate input

is LOW. The flip-flops can also be asynchronously ini-

tialized with the common asynchronous reset and pre-

set product terms.

The buried macrocells are the same as the output

macrocells if they are used for generating logic. In that

case, the only thing that distinguishes them from the

output macrocells is the fact that there is no I/O cell

connection, and the signal is only used internally. The

buried macrocell can also be configured as an input

register or latch.

The I/O Cell

The I/O cell in the MACH211SP consists of a

three-state output buffer. The three-state buffer can be

configured in one of three ways: always enabled, al-

ways disabled, or controlled by a product term. If prod-

uct term control is chosen, one of two product terms

may be used to provide the control. The two product

terms that are available are common to all I/O cells in a

PAL block.

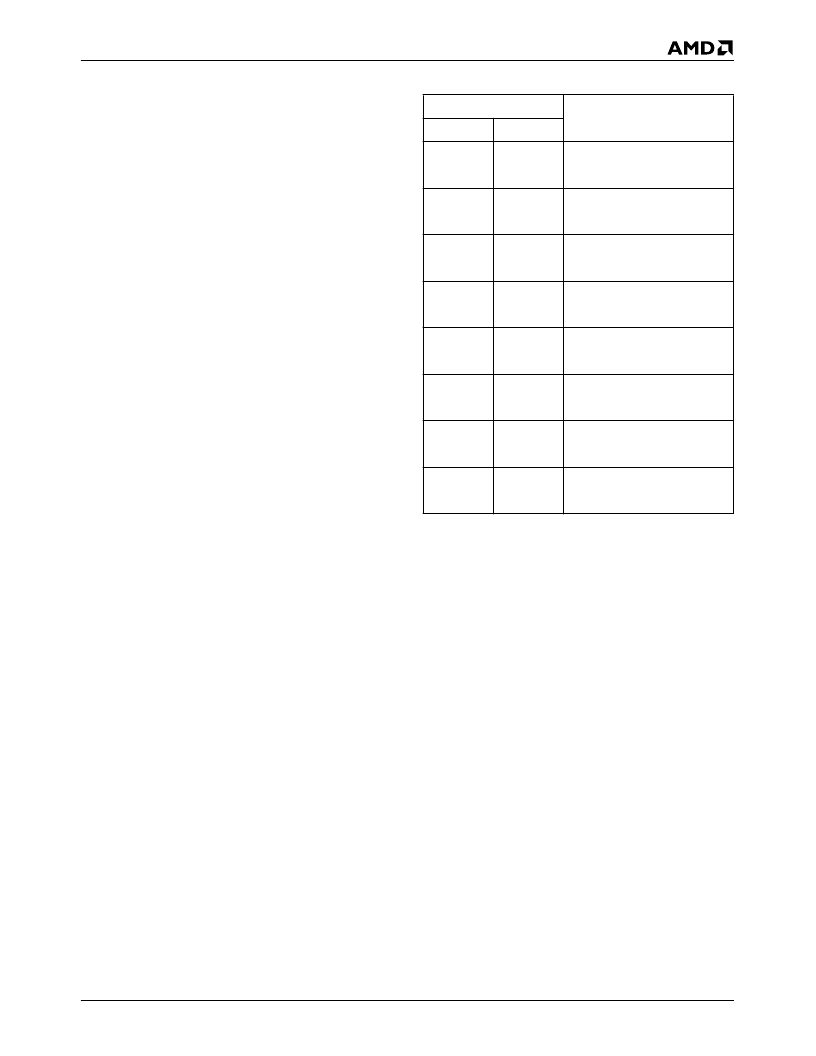

Table 1.

Logic Allocation

Macrocell

Available Clusters

Output

Buried

M

0

C

0

, C

1

, C

2

M

1

C

0

, C

1

, C

2

, C

3

M

2

C

1

,

C

2

,

C

3

,

C

4

M

3

C

2

,

C

3

,

C

4

,

C

5

M

4

C

3

,

C

4

,

C

5

,

C

6

M

5

C

4

,

C

5

,

C

6

,

C

7

M

6

C

5

,

C

6

,

C

7

,

C

8

M

7

C

6

,

C

7

,

C

8

,

C

9

M

8

C

7

,

C

8

,

C

9

,

C

10

M

9

C

8

,

C

9

,

C

10

,

C

11

M

10

C

9

,

C

10

,

C

11

,

C

12

M

11

C

10

,

C

11

,

C

12

,

C

13

M

12

C

11

,

C

12

,

C

13

,

C

14

M

13

C

12

,

C

13

,

C

14

,

C

15

M

14

C

13

,

C

14

,

C

15

M

15

C

14

,

C

15

相关PDF资料 |

PDF描述 |

|---|---|

| MACH211SP-20JC | RES 35.7K-OHM 1% 0.1W 100PPM THICK-FILM SMD-0603 5K/REEL-7IN-PA |

| MACH211SP-20VC | High-Density EE CMOS Programmable Logic |

| MACH211SP-7 | High-Density EE CMOS Programmable Logic |

| MACH211SP-7JC | High-Density EE CMOS Programmable Logic |

| MACH211SP-7VC | High-Density EE CMOS Programmable Logic |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MACH211SP-20JC | 制造商:AMD 制造商全称:Advanced Micro Devices 功能描述:High-Density EE CMOS Programmable Logic |

| MACH211SP-20VC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MACH211SP-6JC | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

| MACH211SP-6VC | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

| MACH211SP-7 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:High-Performance EE CMOS In-System Programmable Logic |

发布紧急采购,3分钟左右您将得到回复。