- 您现在的位置:买卖IC网 > PDF目录17008 > MAX11200EVKIT+ (Maxim Integrated Products)KIT EVALUATION FOR MAX11200 PDF资料下载

参数资料

| 型号: | MAX11200EVKIT+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 22/27页 |

| 文件大小: | 0K |

| 描述: | KIT EVALUATION FOR MAX11200 |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页

4

Maxim Integrated

24-Bit, Single-Channel, Ultra-Low-Power,

Delta-Sigma ADCs with GPIO

MAX11200/MAX11210

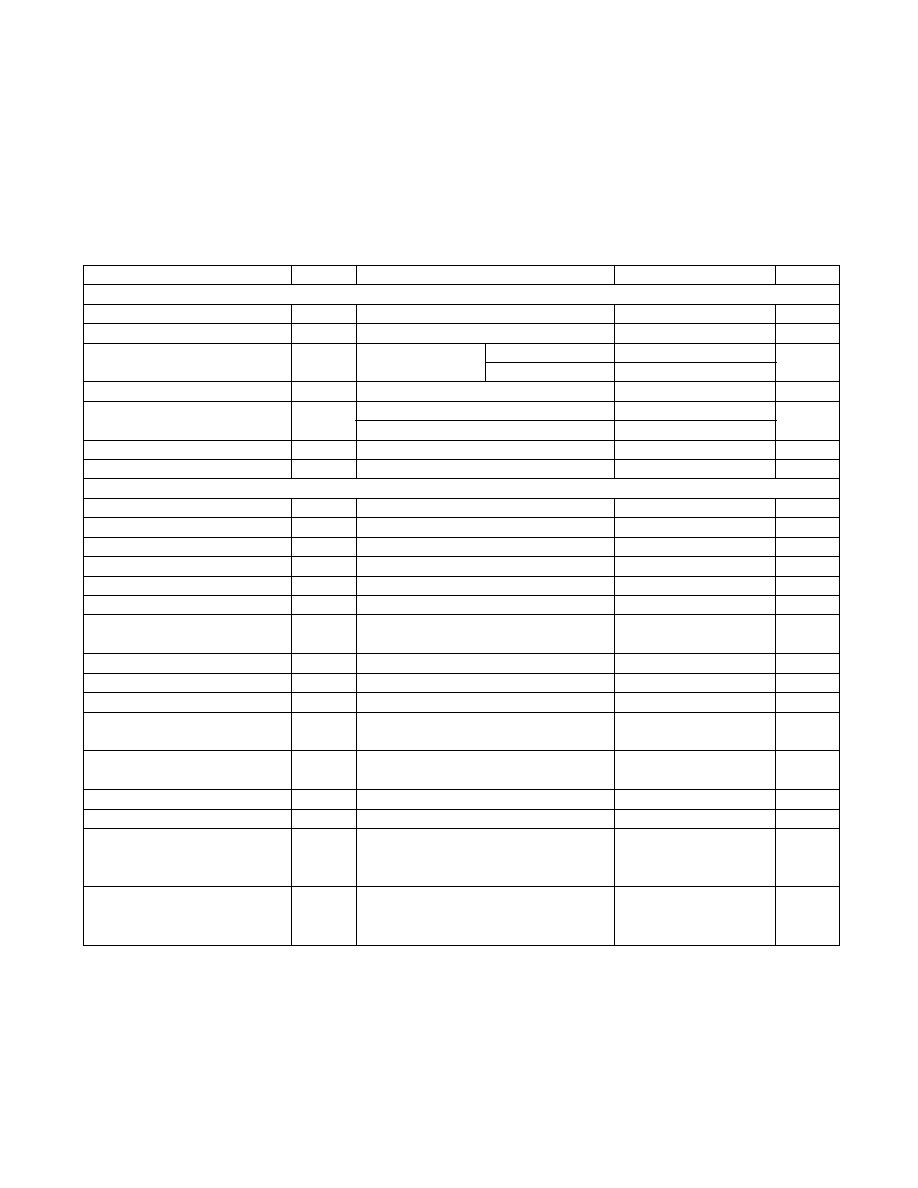

ELECTRICAL CHARACTERISTICS (continued)

(VAVDD = +3.6V, VDVDD = +1.7V, VREFP - VREFN = VAVDD; internal clock, single-cycle mode (SCYCLE = 1), TA = TMIN to TMAX,

unless otherwise noted. Typical values are at TA = +25NC under normal conditions, unless otherwise noted.)

Note 2: These specifications are not fully tested and are guaranteed by design and/or characterization.

Note 3: VAINP = VAINN.

Note 4: ppmFSR is parts per million of full scale.

Note 5: Positive full-scale error includes zero-scale errors (unipolar offset error or bipolar zero error) and applies to both unipolar

and bipolar input ranges.

Note 6: For data rates (1, 2.5, 5, 10, 15)sps and (0.83, 2.08, 4.17, 8.33, 12.5)sps.

Note 7: Normal-mode rejection of power line frequencies of 60Hz/50Hz apply only for single-cycle data rates at 15sps/10sps and

lower or continuous data rate of 60sps/50sps.

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

POWER REQUIREMENTS

Analog Supply

VAVDD

2.7

3.6

V

Digital Supply

VDVDD

1.7

3.6

V

Total Operating Current

AVDD + DVDD

Buffers disabled

235

300

F

A

Buffers enabled

255

AVDD Sleep Current

0.15

2

F

A

AVDD Operating Current

Buffers disabled

185

235

F

A

Buffers enabled

205

DVDD Sleep Current

0.25

2

F

A

DVDD Operating Current

50

65

F

A

SPI TIMING CHARACTERISTICS

SCLK Frequency

fSCLK

5

MHz

SCLK Clock Period

tCP

200

ns

SCLK Pulse-Width High

tCH

80

ns

SCLK Pulse-Width Low

tCL

60% duty cycle at 5MHz

80

ns

CS Low to 1st SCLK Rise Setup

tCSS0

40

ns

CS High to 17th SCLK Setup

tCSS1

40

ns

CS High After 16th SCLK Falling

Edge Hold

tCSH1

3

ns

CS Pulse-Width High

tCSW

40

ns

DIN to SCLK Setup

tDS

40

ns

DIN Hold After SCLK

tDH

0

ns

RDY/DOUT Transition Valid After

SCLK Fall

tDOT

Output transition time, data changes on

falling edge of SCLK

40

ns

RDY/DOUT Remains Valid After

SCLK Fall

tDOH

Output hold time allows for negative edge

data read

3

ns

RDY/DOUT Valid Before SCLK Rise

tDOL

tDOL = tCL - tDOT

40

ns

CS Rise to RDY/DOUT Disable

tDOD

CLOAD = 20pF

25

ns

CS Fall to RDY/DOUT Valid

tDOE

Default value of RDY is 1 for minimum

specification; maximum specification for

valid 0 on RDY/DOUT

0

40

ns

DATA Fetch

tDF

Maximum time after RDY asserts to read

DATA register; tCNV is the time for one

conversion

0

tCNV -

60 x tCP

相关PDF资料 |

PDF描述 |

|---|---|

| HCC06DRTF-S13 | CONN EDGECARD 12POS .100 EXTEND |

| HK1608R47J-T | INDUCTOR HI FREQ 470NH 5% 0603 |

| PCM16XD0 | PROCESSOR MODULE FOR MPLAB-ICE |

| SDR1006-681KL | INDUCTOR POWER 680UH 0.28A SMD |

| 0982660110 | CBL 10POS 0.5MM JMPR TYPE D 8" |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX11200EVKIT+ | 功能描述:数据转换 IC 开发工具 MAX11200 Eval Kit RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

| MAX11201 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:24-Bit, Single-Channel, Ultra-Low-Power, Delta Sigma ADC with 2-Wire Serial Interface |

| MAX11201AEUB+ | 功能描述:模数转换器 - ADC 24-Bit Delta-Sigma RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX11201AEUB+T | 功能描述:模数转换器 - ADC 24-Bit Delta-Sigma RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX11201BEUB+ | 功能描述:模数转换器 - ADC 24-Bit Delta-Sigma RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。