- 您现在的位置:买卖IC网 > PDF目录2008 > MAX1138LEEE+T (Maxim Integrated Products)IC ADC 10BIT SERIAL 16-QSOP PDF资料下载

参数资料

| 型号: | MAX1138LEEE+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 3/22页 |

| 文件大小: | 0K |

| 描述: | IC ADC 10BIT SERIAL 16-QSOP |

| 标准包装: | 2,500 |

| 位数: | 10 |

| 采样率(每秒): | 94.4k |

| 数据接口: | I²C,串行 |

| 转换器数目: | 1 |

| 功率耗散(最大): | 3.35mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SSOP(0.154",3.90mm 宽) |

| 供应商设备封装: | 16-QSOP |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 12 个单端,单极;12 个单端,双极;6 个差分,单极;6 个差分,双极 |

swing from (GND - 0.3V) to (VDD + 0.3V) without caus-

ing damage to the device. For accurate conversions

the inputs must not go more than 50mV below GND or

above VDD.

Single-Ended/Differential Input

The SGL/DIF of the configuration byte configures the

MAX1136–MAX1139 analog-input circuitry for single-

ended or differential inputs (Table 2). In single-ended

mode (SGL/DIF = 1), the digital conversion results are the

difference between the analog input selected by CS[3:0]

and GND (Table 3). In differential mode (SGL/ DIF = 0) the

digital conversion results are the difference between the

“+” and the “-” analog inputs selected by CS[3:0] (Table 4).

Unipolar/Bipolar

When operating in differential mode, the BIP/UNI bit of

the setup byte (Table 1) selects unipolar or bipolar

operation. Unipolar mode sets the differential input

range from 0 to VREF. A negative differential analog

input in unipolar mode will cause the digital output

code to be zero. Selecting bipolar mode sets the differ-

ential input range to ±VREF/2. The digital output code is

binary in unipolar mode and two’s complement in bipo-

lar mode, see the

Transfer Functions section.

In single-ended mode the MAX1136–MAX1139 will

always operate in unipolar mode irrespective of

BIP/UNI. The analog inputs are internally referenced to

GND with a full-scale input range from 0 to VREF.

2-Wire Digital Interface

The MAX1136–MAX1139 feature a 2-wire interface con-

sisting of a serial data line (SDA) and serial clock line

(SCL). SDA and SCL facilitate bidirectional communica-

tion between the MAX1136–MAX1139 and the master at

rates up to 1.7MHz. The MAX1136–MAX1139 are slaves

that transfer and receive data. The master (typically a

microcontroller) initiates data transfer on the bus and

generates the SCL signal to permit that transfer.

SDA and SCL must be pulled high. This is typically done

with pullup resistors (750

or greater) (see the Typical

Operating Circuit). Series resistors (RS) are optional.

They protect the input architecture of the MAX1136–

MAX1139 from high voltage spikes on the bus lines, min-

imize crosstalk, and undershoot of the bus signals.

Bit Transfer

One data bit is transferred during each SCL clock

cycle. A minimum of eighteen clock cycles are required

to transfer the data in or out of the MAX1136–MAX1139.

The data on SDA must remain stable during the high

period of the SCL clock pulse. Changes in SDA while

SCL is stable are considered control signals (see the

START and STOP Conditions section). Both SDA and

SCL remain high when the bus is not busy.

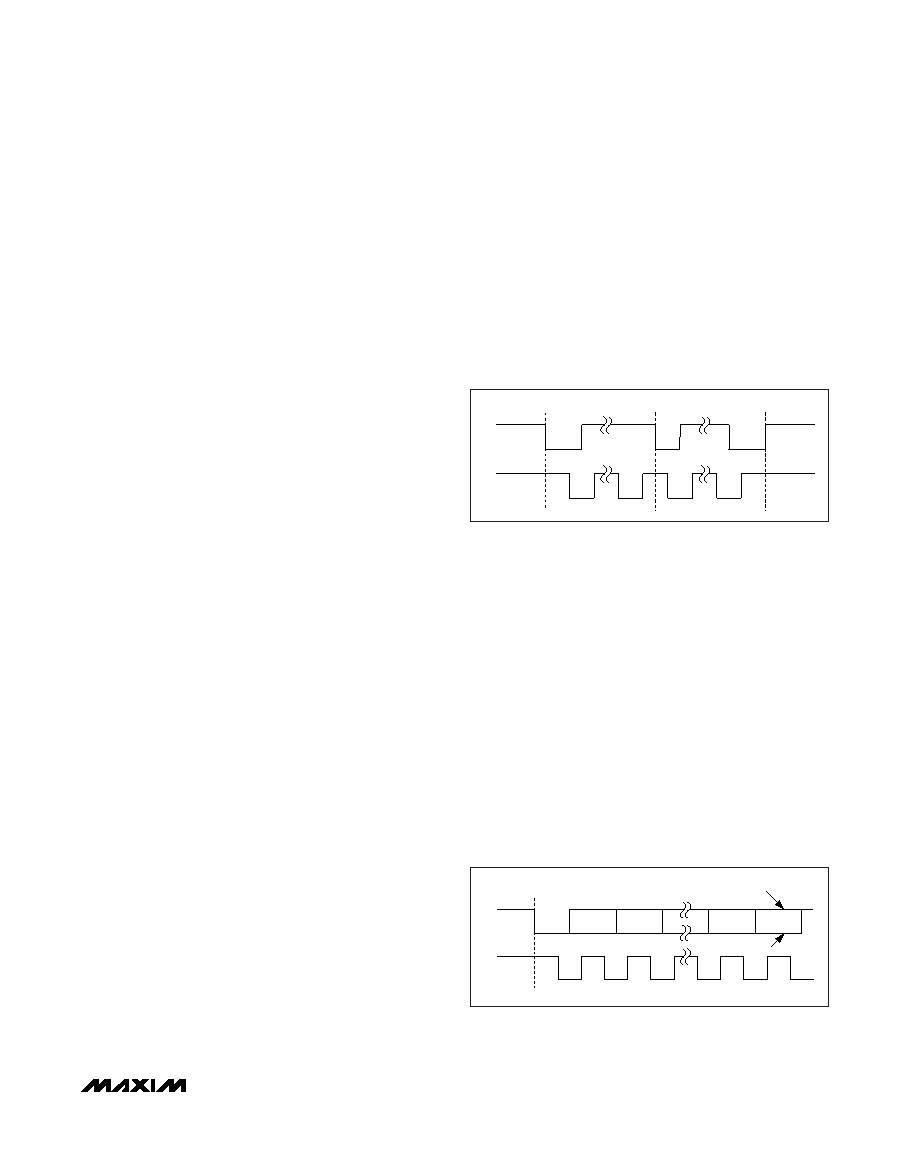

START and STOP Conditions

The master initiates a transmission with a START condi-

tion (S), a high-to-low transition on SDA while SCL is high.

The master terminates a transmission with a STOP condi-

tion (P), a low-to-high transition on SDA while SCL is high

(Figure 5). A repeated START condition (Sr) can be used

in place of a STOP condition to leave the bus active and

the mode unchanged (see HS-mode).

Acknowledge Bits

Data transfers are acknowledged with an acknowledge

bit (A) or a not-acknowledge bit (A). Both the master

and the MAX1136–MAX1139 (slave) generate acknowl-

edge bits. To generate an acknowledge, the receiving

device must pull SDA low before the rising edge of the

acknowledge-related clock pulse (ninth pulse) and

keep it low during the high period of the clock pulse

(Figure 6). To generate a not-acknowledge, the receiv-

er allows SDA to be pulled high before the rising edge

of the acknowledge-related clock pulse and leaves

SDA high during the high period of the clock pulse.

Monitoring the acknowledge bits allows for detection of

unsuccessful data transfers. An unsuccessful data

transfer happens if a receiving device is busy or if a

system fault has occurred. In the event of an unsuc-

cessful data transfer the bus master should reattempt

communication at a later time.

MAX1136–MAX1139

2.7V to 3.6V and 4.5V to 5.5V, Low-Power,

4-/12-Channel, 2-Wire Serial 10-Bit ADCs

______________________________________________________________________________________

11

SCL

SDA

SP

Sr

Figure 5. START and STOP Conditions

SCL

SDA

S

NOT ACKNOWLEDGE

ACKNOWLEDGE

12

8

9

Figure 6. Acknowledge Bits

相关PDF资料 |

PDF描述 |

|---|---|

| MAX1159AEUI+ | IC ADC 14BIT 135KSPS 28-TSSOP |

| MAX11602EEE+ | IC ADC SERIAL 8BIT 8CH 16-QSOP |

| MAX11610EEE+T | IC ADC SERIAL 10BIT 12CH 16-QSOP |

| MAX11616EEE+T | IC ADC SERIAL 12BIT 12CH 16-QSOP |

| MAX1162AEUB+T | IC ADC 16BIT 200KSPS 10-MSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX1138MEEE | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX1138MEEE+ | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX1138MEEE+T | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX1138MEEE-T | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX1139 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:2.7V to 3.6V and 4.5V to 5.5V, Low-Power, 4-/12-Channel, 2-Wire Serial 10-Bit ADCs |

发布紧急采购,3分钟左右您将得到回复。