- 您现在的位置:买卖IC网 > PDF目录9882 > MAX1167BCEE+T (Maxim Integrated Products)IC ADC 16BIT 200KSPS 16-QSOP PDF资料下载

参数资料

| 型号: | MAX1167BCEE+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 9/30页 |

| 文件大小: | 0K |

| 描述: | IC ADC 16BIT 200KSPS 16-QSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 位数: | 16 |

| 采样率(每秒): | 200k |

| 数据接口: | MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 667mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-SSOP(0.154",3.90mm 宽) |

| 供应商设备封装: | 16-QSOP |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 4 个单端,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

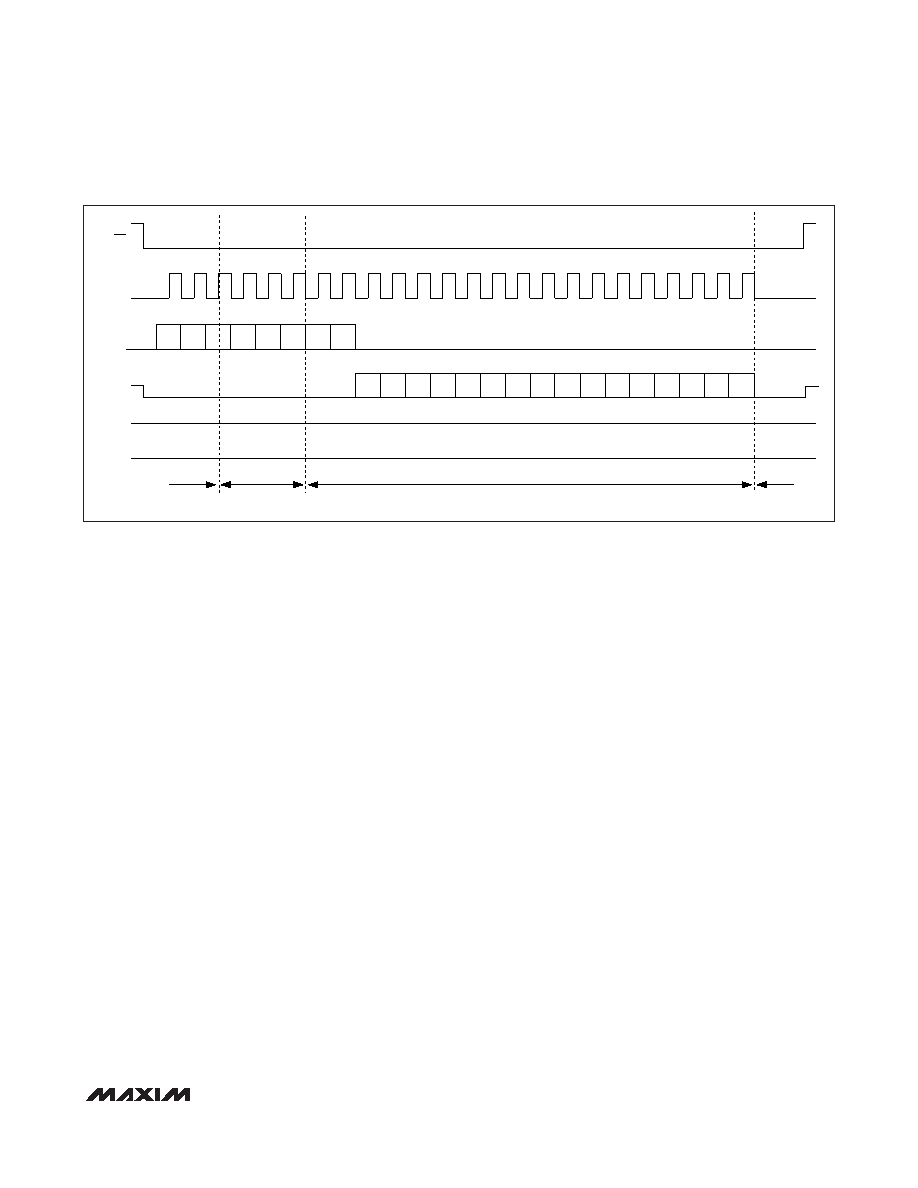

SCLK rates less than 125kHz can reduce accuracy due

to leakage of the sampling capacitor. DOUT changes

from high-Z to logic low after CS is brought low. Input

data latches on the rising edge of SCLK. The first SCLK

rising edge begins loading data into the command/con-

figuration/control register from DIN. The devices select

the proper channel for conversion on the rising edge of

the 3rd SCLK cycle. Acquisition begins immediately

thereafter and ends on the falling edge of the 6th clock

cycle. The MAX1167/MAX1168 sample the input and

begin conversion on the falling edge of the 6th clock

cycle.

Setup

and

configuration

of

the

MAX1167/MAX1168 complete on the rising edge of the

8th clock cycle. The conversion result is available (MSB

first) at DOUT on the falling edge of the 8th SCLK cycle.

To read the entire conversion result, 16 SCLK cycles are

needed. Extra clock pulses, occurring after the conver-

sion result has been clocked out and prior to the rising

edge of CS, cause zeros to be clocked out of DOUT.

The MAX1167/ MAX1168 external clock 8-bit-wide data-

transfer mode requires 24 SCLK cycles for completion

(Figure 10).

Force CS high after the conversion result is read. For

maximum throughput, force CS low again to initiate the

next conversion immediately after the specified mini-

mum time (tCSW). Forcing CS high in the middle of a

conversion immediately aborts the conversion and

places the MAX1167/MAX1168 in shutdown.

External Clock 16-Bit-Wide Data-Transfer Mode

(MAX1168 Only)

Force DSPR high and DSEL high for SPI/QSPI/

MICROWIRE interface mode. Logic high at DSEL allows

the MAX1168 to transfer data in 16-bit-wide words. The

acquisition time is extended an extra eight SCLK cycles

in the 16-bit-wide data-transfer mode. The falling edge of

CS wakes the analog circuitry and allows SCLK to clock

in data. Ensure the duty cycle on SCLK is between 45%

and 55% when operating at 4.8MHz (the maximum clock

frequency). For lower clock frequencies, ensure that the

minimum high and low times are at least 93ns. External-

clock-mode conversions with SCLK rates less than

125kHz can reduce accuracy due to leakage of the sam-

pling capacitor. DOUT changes from high-Z to logic low

after CS is brought low. Input data latches on the rising

edge of SCLK. The first SCLK rising edge begins loading

data into the command/configuration/control register from

DIN. The devices select the proper channel for conver-

sion and begin acquisition on the rising edge of the 3rd

SCLK cycle. Setup and configuration of the MAX1168

completes on the rising edge of the 8th clock cycle.

Acquisition ends on the falling edge of the 14th SCLK

cycle. The MAX1168 samples the input and begins con-

version on the falling edge of the 14th clock cycle. The

conversion result is available (MSB first) at DOUT on the

falling edge of the 16th SCLK cycle. To read the entire

conversion result, 16 SCLK cycles are needed. Extra

clock pulses, occurring after the conversion result has

been clocked out and prior to the rising edge of CS,

cause zeros to be clocked out of DOUT.

MAX1167/MAX1168

Multichannel, 16-Bit, 200ksps Analog-to-Digital

Converters

______________________________________________________________________________________________________

17

DOUT

CS

SCLK

DIN

DSPR*

*MAX1168 ONLY

0

MSB

LSB

MSB

LSB

tACQ

IDLE

tCONV

ADC

STATE

1

8

16

DSEL*

24

Figure 10. SPI External Clock Mode, 8-Bit Data-Transfer Mode, Conversion Timing

相关PDF资料 |

PDF描述 |

|---|---|

| MAX1248AEPE+ | IC ADC 10BIT SERIAL 16-DIP |

| MS27484T18A32SA | CONN PLUG 32POS STRAIGHT W/SCKT |

| MAX111BEAP+ | IC ADC 14BIT 2CH 20SSOP |

| MS27508E24B61SB | CONN RCPT 61POS BOX MNT W/SCKT |

| MAX1092AEEG+ | IC ADC 10BIT 400KSPS 24-QSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX1167BEEE | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX1167BEEE+ | 功能描述:模数转换器 - ADC 16-Bit 4Ch 200ksps 5.25V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX1167BEEE+T | 功能描述:模数转换器 - ADC 16-Bit 4Ch 200ksps 5.25V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX1167BEEE-T | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX1167CCEE | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。