- 您现在的位置:买卖IC网 > PDF目录9951 > MAX1322ECM+T (Maxim Integrated Products)IC ADC 14BIT 2CH 900KSPS 48LQFP PDF资料下载

参数资料

| 型号: | MAX1322ECM+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 9/27页 |

| 文件大小: | 0K |

| 描述: | IC ADC 14BIT 2CH 900KSPS 48LQFP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,000 |

| 位数: | 14 |

| 采样率(每秒): | 900k |

| 数据接口: | 并联 |

| 转换器数目: | 1 |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 48-LQFP |

| 供应商设备封装: | 48-LQFP(7x7) |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 2 个单端,双极 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

MAX1316–MAX1318/MAX1320–MAX1322/MAX1324–MAX1326

8-/4-/2-Channel, 14-Bit, Simultaneous-Sampling ADCs

with ±10V, ±5V, and 0 to +5V Analog Input Ranges

______________________________________________________________________________________

17

Data Throughput

The data throughput (fTH) of the MAX1316–MAX1318/

MAX1320–MAX1322/MAX1324–MAX1326 is a function

of the clock speed (fCLK). In internal-clock mode, fCLK =

10MHz. In external-clock mode, 100kHz ≤ fCLK ≤

12.5MHz. When reading during conversion (Figures 5

and 6), calculate fTH as follows:

where N is the number of active channels and tQUIET

includes acquistion time tACQ. tQUIET is the period of bus

inactivity before the rising edge of CONVST. Typically use

tQUIET = tACQ + 50ns, and prevent disturbance on the

output bus from corrupting signal acquistion. See the

Starting a Conversion section for more information.

Reading a Conversion Result

Reading During a Conversion

Figures 5 and 6 show the interface signals for initiating a

read operation during a conversion cycle. These figures

show two channels selected for conversion. If more chan-

nels are selected, the results are available successively

every third clock cycle. CS can be low at all times; it can

be low during the RD cycles, or it can be the same as RD.

After initiating a conversion by bringing CONVST high,

wait for EOC to go low (about 1.6s in internal-clock

mode or 17 clock cycles in external-clock mode) before

reading the first conversion result. Read the conversion

result by bringing RD low, thus latching the data to the

parallel digital-output bus. Bring RD high to release the

digital bus. Wait for the next falling edge of EOC (about

300ns in internal-clock mode or three clock cycles in

external-clock mode) before reading the next result.

When the last result is available, EOLC goes low.

f

t

xN

f

TH

QUIET

CLK

=

+

+

1

16

3

1

()

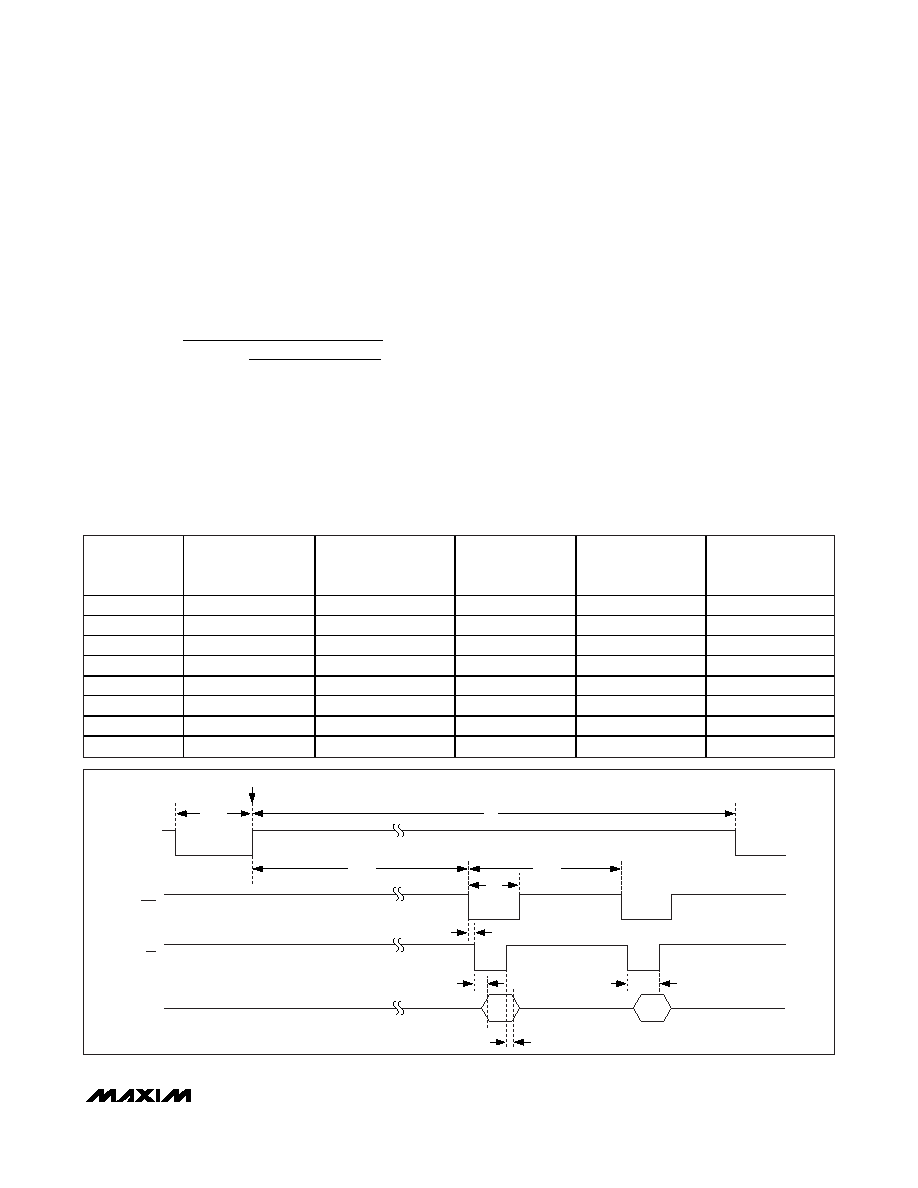

Table 3. Throughput vs. Channels Sampled (tQUIET = tACQ = 200ns, fCLK = 10MHz)

CHANNELS

SAMPLED

(N)

CLOCK CYCLES

UNTIL LAST

RESULT

CLOCK CYCLE FOR

READING LAST

CONVERSION

TOTAL

CONVERSION

TIME (ns)

SAMPLES PER

SECOND

(ksps)

THROUGHPUT

PER CHANNEL

(ksps)

1

16

1

1900

526

2

19

1

2200

909

455

3

22

1

2500

1200

400

4

25

1

2800

1429

357

5

28

1

3100

1613

323

6

31

1

3400

1765

294

7

34

1

3700

1892

270

8

37

1

4000

2000

250

Figure 5. Read During Conversion—Two Channels Selected, Internal Clock

CONVST

CH0

TRACK

HOLD

D0–D13

SAMPLE

t1

t13

t12

t10

t3

t11

TRACK

CH1

tCONV

tNEXT

EOC

RD

t20

相关PDF资料 |

PDF描述 |

|---|---|

| IDT72V3660L6PF | IC FIFO SS 4096X36 6NS 128-TQFP |

| MS27466T15B37P | CONN RCPT 37POS WALL MT W/PINS |

| IDT72V3660L6BB | IC FIFO SS 4096X36 6NS 144-BGA |

| MAX1318ECM+T | IC ADC 14BIT 2CH 900KSPS 48LQFP |

| IDT72T3665L6-7BB | IC FIFO 4096X36 6-7NS 208-BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX13234EAUP+ | 功能描述:RS-232接口集成电路 3-5.5V 250Kbps RS232 Line Driver/Receiver RoHS:否 制造商:Exar 数据速率:52 Mbps 工作电源电压:5 V 电源电流:300 mA 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体:LQFP-100 封装: |

| MAX13234EAUP+T | 功能描述:RS-232接口集成电路 3-5.5V 250Kbps RS232 Line Driver/Receiver RoHS:否 制造商:Exar 数据速率:52 Mbps 工作电源电压:5 V 电源电流:300 mA 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体:LQFP-100 封装: |

| MAX13234EETP | 功能描述:RS-232接口集成电路 RoHS:否 制造商:Exar 数据速率:52 Mbps 工作电源电压:5 V 电源电流:300 mA 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体:LQFP-100 封装: |

| MAX13234EETP+ | 功能描述:RS-232接口集成电路 3-5.5V 250Kbps RS232 Line Driver/Receiver RoHS:否 制造商:Exar 数据速率:52 Mbps 工作电源电压:5 V 电源电流:300 mA 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体:LQFP-100 封装: |

| MAX13234EETP+T | 功能描述:RS-232接口集成电路 3-5.5V 250Kbps RS232 Line Driver/Receiver RoHS:否 制造商:Exar 数据速率:52 Mbps 工作电源电压:5 V 电源电流:300 mA 工作温度范围:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体:LQFP-100 封装: |

发布紧急采购,3分钟左右您将得到回复。