- 您现在的位置:买卖IC网 > PDF目录9466 > MAX1346BETX+T (Maxim Integrated Products)IC ADC/DAC 12BIT W/FIFO 36WQFN PDF资料下载

参数资料

| 型号: | MAX1346BETX+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 4/39页 |

| 文件大小: | 0K |

| 描述: | IC ADC/DAC 12BIT W/FIFO 36WQFN |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 类型: | ADC,DAC |

| 分辨率(位): | 12 b |

| 采样率(每秒): | 225k |

| 数据接口: | MICROWIRE?,QSPI?,串行,SPI? |

| 电压电源: | 模拟和数字 |

| 电源电压: | 4.75 V ~ 5.25 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 36-WFQFN 裸露焊盘 |

| 供应商设备封装: | 36-TQFN 裸露焊盘(6x6) |

| 包装: | 带卷 (TR) |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页

MAX1340/MAX1342/MAX1346/MAX1348

12-Bit, Multichannel ADCs/DACs with FIFO,

Temperature Sensing, and GPIO Ports

12

______________________________________________________________________________________

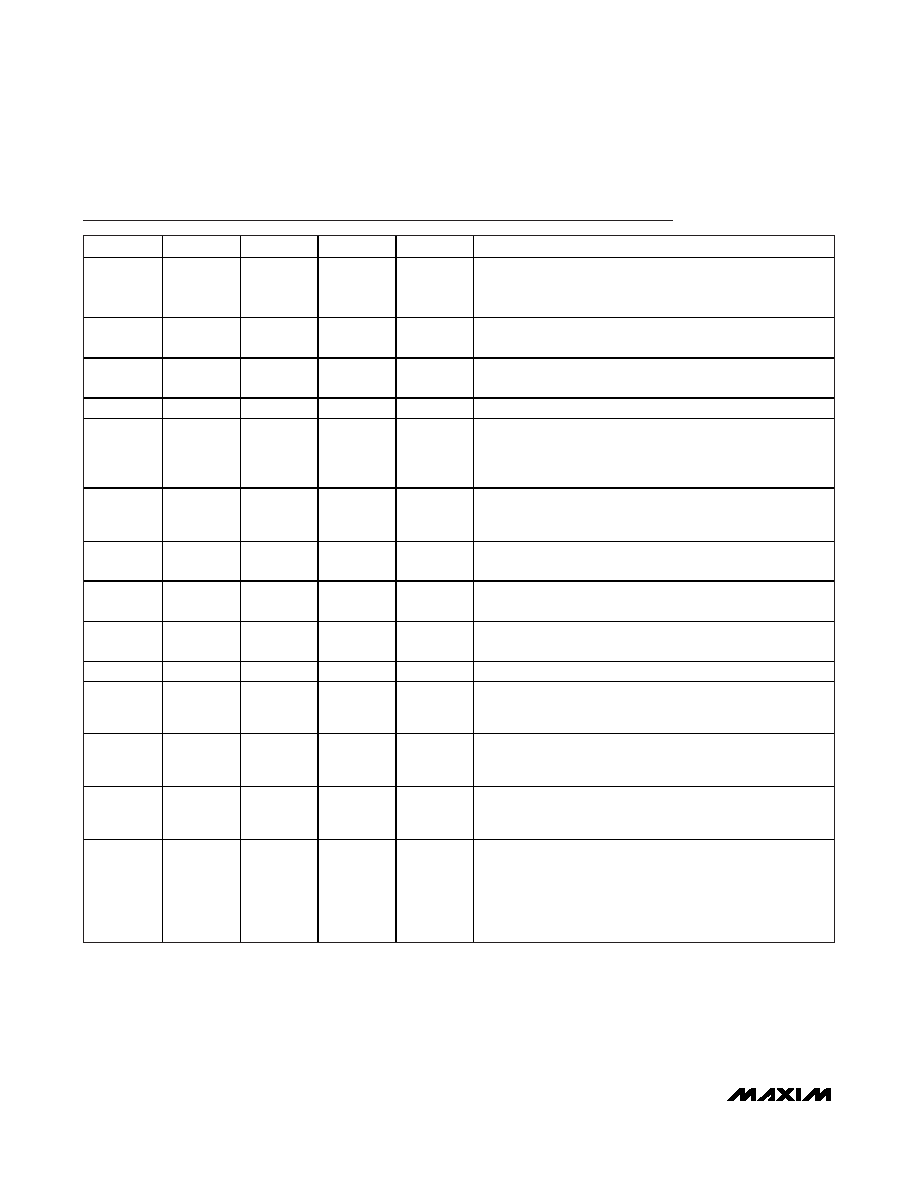

Pin Description

MAX1340

MAX1342

MAX1346

MAX1348

NAME

FUNCTION

1, 2, 16–19,

24, 25

16–19

1, 2, 16–19,

24, 25, 31,

34

16–19, 31,

34

D.C.

Do Not Connect. Do not connect to this pin.

3

333

EOC

Active-Low End-of-Conversion Output. Data is valid after the

falling edge of

EOC.

4

444

DVDD

Digital Positive Power Input. Bypass DVDD to DGND with a

0.1F capacitor.

5

DGND

Digital Ground. Connect DGND to AGND.

6

DOUT

Serial Data Output. Data is clocked out on the falling edge of

the SCLK clock in clock modes 00, 01, and 10. Data is

clocked out on the rising edge of the SCLK clock in clock

mode 11. High impedance when

CS is high.

7

SCLK

Serial Clock Input. Clocks data in and out of the serial

interface. (Duty cycle must be 40% to 60%.) See Table 4 for

details on programming the clock mode.

8

888

DIN

Serial Data Input. DIN data is latched into the serial interface

on the falling edge of SCLK.

9–12

OUT0–

OUT3

DAC Outputs

13

AVDD

Positive Analog Power Input. Bypass AVDD to AGND with a

0.1F capacitor.

14

AGND

Analog Ground

15, 23, 32,

33

15, 23, 32,

33

15, 23, 32,

33

15, 23, 32,

33

N.C.

No Connection. Not internally connected.

20

LDAC

Active-Low Load DAC.

LDAC is an asynchronous active-low

input that updates the DAC outputs. Drive

LDAC low to make

the DAC registers transparent.

21

CS

Active-Low Chip-Select Input. When

CS is low, the serial

interface is enabled. When

CS is high, DOUT is high

impedance.

22

RES_SEL

Reset Select. Selects DAC wake-up mode. Set RES_SEL low

to wake up the DAC outputs with a 100k

resistor to GND or

set RES_SEL high to wake up the DAC outputs with a 100k

resistor to VREF. Set RES_SEL high to power up the DAC input

register to FFFh. Set RES_SEL low to power up the DAC input

register to 000h.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-254-MY-S | CONVERTER MOD DC/DC 48V 50W |

| LTC6990HS6#TRPBF | IC OSC SILICON 1MHZ TSOT23-6 |

| LTC6990HDCB#TRPBF | IC OSC SILICON 1MHZ 6DFN |

| V375B15M300BF | CONVERTER MOD DC/DC 15V 300W |

| LTC6992HDCB-4#TRMPBF | IC OSC SILICON 1MHZ 6-DFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX1347BETX | 制造商:Maxim Integrated Products 功能描述:12-BIT, MULTICHANNEL ADCS/DACS WITH FIFO, TEM - Rail/Tube |

| MAX1347BETX+ | 制造商:Maxim Integrated Products 功能描述:12-BIT MULTICHANNEL ADCS/DACS WITH - Rail/Tube |

| MAX1347BETX+T | 制造商:Maxim Integrated Products 功能描述:12-BIT MULTICHANNEL ADCS/DACS WITH - Tape and Reel |

| MAX1347BETX-T | 制造商:Maxim Integrated Products 功能描述:12-BIT, MULTICHANNEL ADCS/DACS WITH FIFO, TEM - Tape and Reel |

| MAX13481EETE | 功能描述:USB 接口集成电路 RoHS:否 制造商:Cypress Semiconductor 产品:USB 2.0 数据速率: 接口类型:SPI 工作电源电压:3.15 V to 3.45 V 工作电源电流: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:WLCSP-20 |

发布紧急采购,3分钟左右您将得到回复。