- 您现在的位置:买卖IC网 > PDF目录9906 > MAX157AEPA+ (Maxim Integrated Products)IC ADC 10BIT 108KSPS 2CH 8-DIP PDF资料下载

参数资料

| 型号: | MAX157AEPA+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 15/16页 |

| 文件大小: | 0K |

| 描述: | IC ADC 10BIT 108KSPS 2CH 8-DIP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 50 |

| 位数: | 10 |

| 采样率(每秒): | 108k |

| 数据接口: | MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 727mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 通孔 |

| 封装/外壳: | 8-DIP(0.300",7.62mm) |

| 供应商设备封装: | 8-PDIP |

| 包装: | 管件 |

| 输入数目和类型: | 2 个单端,单极 |

MAX157/MAX159

+2.7V, Low-Power, 2-Channel,

108ksps, Serial 10-Bit ADCs in 8-Pin MAX

8

_______________________________________________________________________________________

The capacitive digital-to-analog converter (DAC)

adjusts during the remainder of the conversion cycle

to restore node ZERO to 0V within the limits of 10-bit

resolution. This action is equivalent to transferring a

16pF [(VIN+) - (VIN-)] charge from CHOLD to the bina-

ry-weighted capacitive DAC, which in turn forms a digi-

tal representation of the analog input signal.

Track/Hold

The ADC’s T/H stage enters its tracking mode on the

falling edge of CS/SHDN. For the MAX157 (single-

ended inputs), IN- is connected to GND and the con-

verter samples the positive (“+”) input. For the MAX159

(pseudo-differential inputs), IN- connects to the nega-

tive input (“-”), and the difference of [(VIN+) - (VIN-)] is

sampled. At the end of the conversion, the positive

input connects back to IN+ and CHOLD charges to the

input signal.

The time required for the T/H stage to acquire an input

signal is a function of how fast its input capacitance is

charged. If the input signal’s source impedance is high,

the acquisition time lengthens and more time must be

allowed between conversions. The acquisition time,

tACQ, is the maximum time the device takes to acquire

the signal, and is also the minimum time required for

the signal to be acquired. Calculate this with the follow-

ing equation:

tACQ = 7(RS + RIN)CIN

where RS is the source impedance of the input signal,

RIN (9k) is the input resistance, and CIN (16pF) is the

input capacitance of the ADC. Source impedances

below 4k

have no significant impact on the AC perfor-

mance of the MAX157/MAX159.

Higher source impedances can be used if a 0.01F

capacitor is connected to the individual analog inputs.

Together with the input impedance, this capacitor forms

an RC filter, limiting the ADC’s signal bandwidth.

Input Bandwidth

The MAX157/MAX159 T/H stage offers both a 2.25MHz

small-signal and a 1MHz full-power bandwidth, which

makes it possible to use the parts for digitizing high-

speed transients and measuring periodic signals with

bandwidths exceeding the ADC’s sampling rate by

using undersampling techniques. To avoid high-fre-

quency signals being aliased into the frequency band

of interest, anti-alias filtering is recommended. Most

aliasing problems can be fixed easily with an external

resistor and a capacitor. However, if DC precision is

required, it is usually best to choose a continuous

or switched-capacitor filter, such as the MAX7410/

MAX7414 (Figure 4). Their Butterworth characteristic

generally provides the best compromise (with regard to

rolloff and attenuation) in filter configurations, is easy to

design, and provides a maximally flat passband re-

sponse.

Analog Input Protection

Internal protection diodes, which clamp the analog

input to VDD and GND, allow each input channel to

swing within GND - 300mV to VDD + 300mV without

damage. However, for accurate conversions both

inputs must not exceed VDD + 50mV or be less than

GND - 50mV.

If an off-channel analog input voltage exceeds the

supplies, limit the input current to 4mA.

MAX157

MAX159

10+2 BIT

SAR

ADC

SCLK

IN

OUT

ANALOG

INPUT

MUX

(2 CHANNEL)

CH0

(CH+)

CH1

(CH-)

REF

( ) ARE FOR MAX159

T/H

CONTROL

LOGIC

SCLK

CS/SHDN

INTERNAL

CLOCK

OUTPUT

REGISTER

DOUT

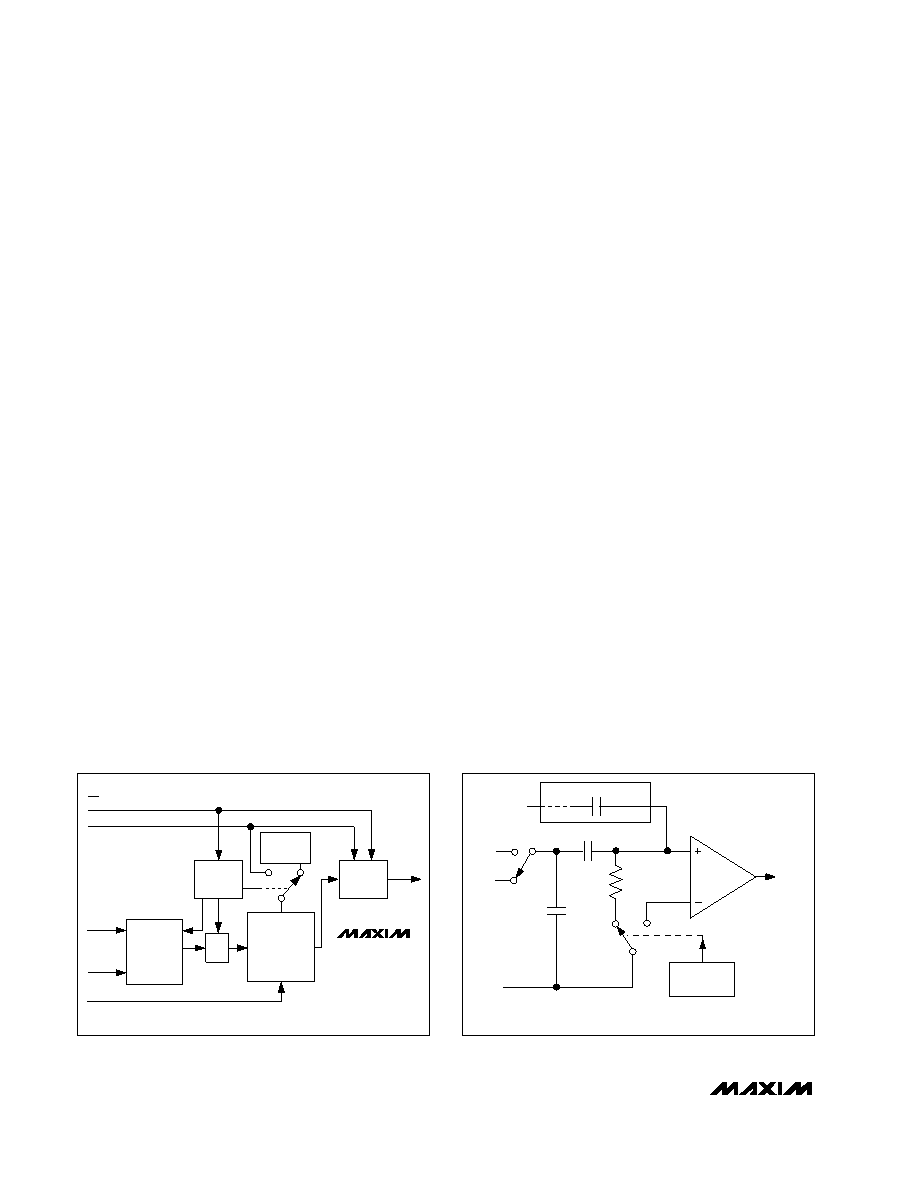

Figure 2. MAX157/MAX159 Simplified Functional Diagram

CH0

(CH+)

CH1

(CH-)

GND

CSWITCH

TRACK

T/H

RIN

9k

HOLD

CAPACITIVE DAC

CONTROL

LOGIC

REF

ZERO

TO SAR

( ) ARE FOR MAX159

COMPARATOR

–

+

CHOLD

16pF

SINGLE-ENDED MODE: CHO, CH1 = IN+; GND = IN-

DIFFERENTIAL MODE: CH+ = IN+; CH- = IN-

INPUT

MUX

Figure 3. Analog Input Channel Structure

相关PDF资料 |

PDF描述 |

|---|---|

| MC33897CTEF | IC TRANSCEIVER CAN SW 14SOIC |

| IDT72V36100L7-5PF | IC FIFO 64X36 7-5NS 128QFP |

| MAX1301BEUP+T | IC ADC 16BIT SER 4CH LP 20TSSOP |

| IDT723662L12PF | IC FIFO BI SYNC 8192X36 120QFP |

| MAX1303BEUP+T | IC ADC 16BIT MULT RANGE 20TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX157AEPA+ | 功能描述:模数转换器 - ADC 10-Bit 2Ch 108ksps 5.25V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX157AEUA | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX157AEUA+ | 功能描述:模数转换器 - ADC 10-Bit 2Ch 108ksps 5.25V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX157AEUA+T | 功能描述:模数转换器 - ADC 10-Bit 2Ch 108ksps 5.25V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| MAX157AEUA-T | 功能描述:模数转换器 - ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。