- 您现在的位置:买卖IC网 > PDF目录16551 > MAX1587AETL+T (Maxim Integrated Products)IC POWER MANAGEMENT 40-TQFN PDF资料下载

参数资料

| 型号: | MAX1587AETL+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 23/30页 |

| 文件大小: | 0K |

| 描述: | IC POWER MANAGEMENT 40-TQFN |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 应用: | 手持/移动设备 |

| 电源电压: | 2.6 V ~ 5.5 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 40-WFQFN 裸露焊盘 |

| 供应商设备封装: | 40-TQFN-EP(6x6) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页当前第23页第24页第25页第26页第27页第28页第29页第30页

�� �

�

�

�High-Efficiency,� Low-I� Q� PMICs� with�

�Dynamic� Core� for� PDAs� and� Smart� Phones�

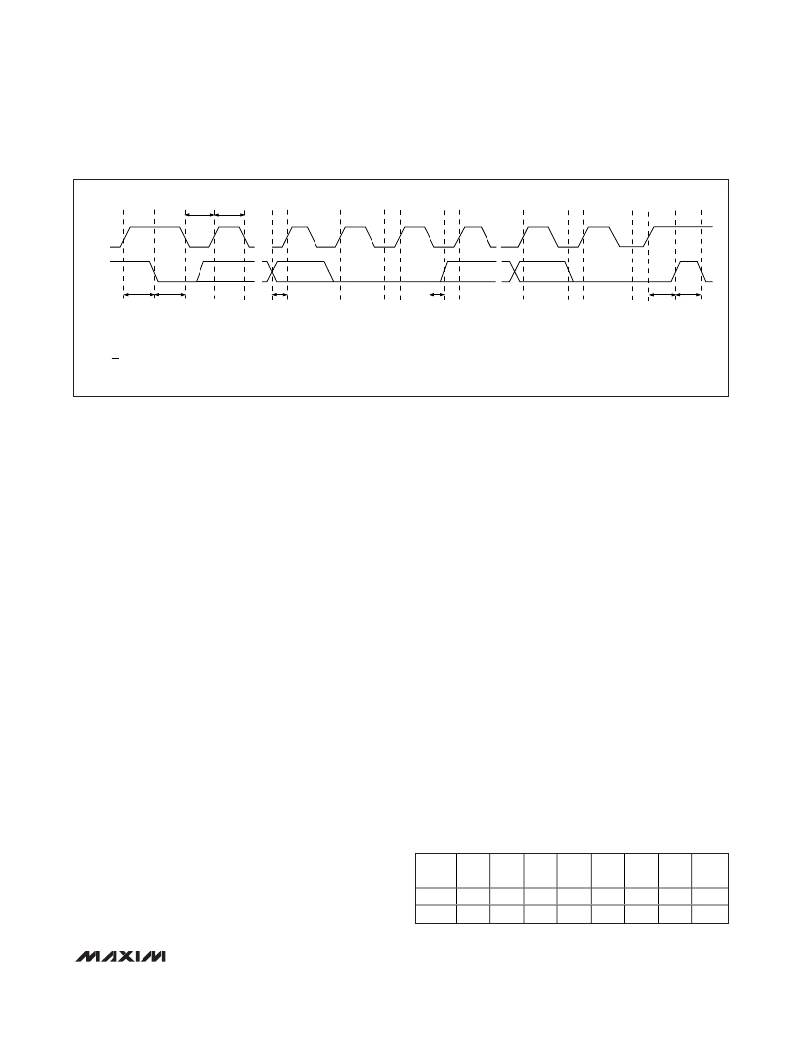

�A�

�t� LOW�

�B�

�t� HIGH�

�C�

�D�

�E�

�F�

�G�

�H�

�I�

�J�

�K�

�L�

�M�

�SCL�

�SDA�

�t� SU:STA�

�t� HD:STA�

�t� SU:DAT�

�t� HD:DAT�

�t� SU:STO� t� BUF�

�A� =� START� CONDITION�

�B� =� MSB� OF� ADDRESS� CLOCKED� INTO� SLAVE�

�C� =� LSB� OF� ADDRESS� CLOCKED� INTO� SLAVE�

�D� =� R/W� BIT� CLOCKED� INTO� SLAVE�

�F� =� ACKNOWLEDGE� BIT� CLOCKED� INTO� MASTER�

�G� =� MSB� OF� DATA� CLOCKED� INTO� SLAVE� (OP/SUS� BIT)�

�H� =� LSB� OF� DATA� CLOCKED� INTO� SLAVE�

�I� =� SLAVE� PULLS� SMB� DATA� LINE� LOW�

�J� =� ACKNOWLEDGE� CLOCKED� INTO� MASTER�

�K� =� ACKNOWLEDGE� CLOCK� PULSE�

�L� =� STOP� CONDITION,� DATA� EXECUTED� BY� SLAVE�

�M� =� NEW� START� CONDITION�

�E� =� SLAVE� PULLS� SMB� DATA� LINE� LOW�

�Figure� 5.� I� 2� C-Compatible� Serial-Interface� Timing� Diagram�

�The� serial� interface� consists� of� a� serial� data� line� (SDA)�

�and� a� serial� clock� line� (SCL).� Standard� I� 2� C-compatible�

�write-byte� commands� are� used.� Figure� 5� shows� a� tim-�

�ing� diagram� for� the� I� 2� C� protocol.� The� MAX1586/�

�MAX1587� are� slave-only� devices,� relying� upon� a� master�

�to� generate� a� clock� signal.� The� master� (typically� a�

�microprocessor)� initiates� data� transfer� on� the� bus� and�

�generates� SCL� to� permit� data� transfer.� A� master� device�

�communicates� to� the� MAX1586/MAX1587� by� transmit-�

�ting� the� proper� address� followed� by� the� 8-bit� data� code�

�(Table� 2).� Each� transmit� sequence� is� framed� by� a�

�START� (A)� condition� and� a� STOP� (L)� condition.� Each�

�word� transmitted� over� the� bus� is� 8� bits� long� and� is�

�always� followed� by� an� acknowledge� clock� pulse.�

�Table� 2� shows� the� serial� data� codes� used� to� program�

�V3� and� V6.� The� default� power-up� voltage� for� V3� is� 1.3V�

�and� for� V6� is� 0V.�

�Bit� Transfer�

�One� data� bit� is� transferred� during� each� SCL� clock�

�cycle.� The� data� on� SDA� must� remain� stable� during� the�

�high� period� of� the� SCL� clock� pulse.� Changes� in� SDA�

�while� SCL� is� high� are� control� signals� (see� the� START�

�and� STOP� Conditions� section).� Both� SDA� and� SCL� idle�

�high� when� the� bus� is� not� busy.�

�START� and� STOP� Conditions�

�When� the� serial� interface� is� inactive,� SDA� and� SCL� idle�

�high.� A� master� device� initiates� communication� by� issu-�

�ing� a� START� condition.� A� START� condition� is� a� high-to-�

�low� transition� on� SDA� with� SCL� high.� A� STOP� condition�

�(see� the� Acknowledge� Bit� (ACK)� section).� The� STOP�

�condition� frees� the� bus.�

�When� a� STOP� condition� or� incorrect� address� is� detect-�

�ed,� the� MAX1586/MAX1587� internally� disconnect� SCL�

�from� the� serial� interface� until� the� next� START� condition,�

�minimizing� digital� noise� and� feedthrough.�

�Acknowledge� Bit� (ACK)�

�The� acknowledge� bit� (ACK)� is� the� ninth� bit� attached� to�

�every� 8-bit� data� word.� The� receiving� device� always�

�generates� ACK.� The� MAX1586/MAX1587� generate� an�

�ACK� when� receiving� an� address� or� data� by� pulling� SDA�

�low� during� the� ninth� clock� period.� Monitoring� ACK�

�allows� for� detection� of� unsuccessful� data� transfers.� An�

�unsuccessful� data� transfer� occurs� if� a� receiving� device�

�is� busy� or� if� a� system� fault� has� occurred.� In� the� event� of�

�an� unsuccessful� data� transfer,� the� bus� master� should�

�reattempt� communication� at� a� later� time.�

�Serial� Address�

�A� bus� master� initiates� communication� with� a� slave�

�device� by� issuing� a� START� condition� followed� by� the�

�7-bit� slave� address� (Table� 3).� When� idle,� the�

�MAX1586/MAX1587� wait� for� a� START� condition� fol-�

�lowed� by� its� slave� address.� The� serial� interface� com-�

�pares� each� address� value� bit� by� bit,� allowing� the�

�interface� to� power� down� immediately� if� an� incorrect�

�address� is� detected.�

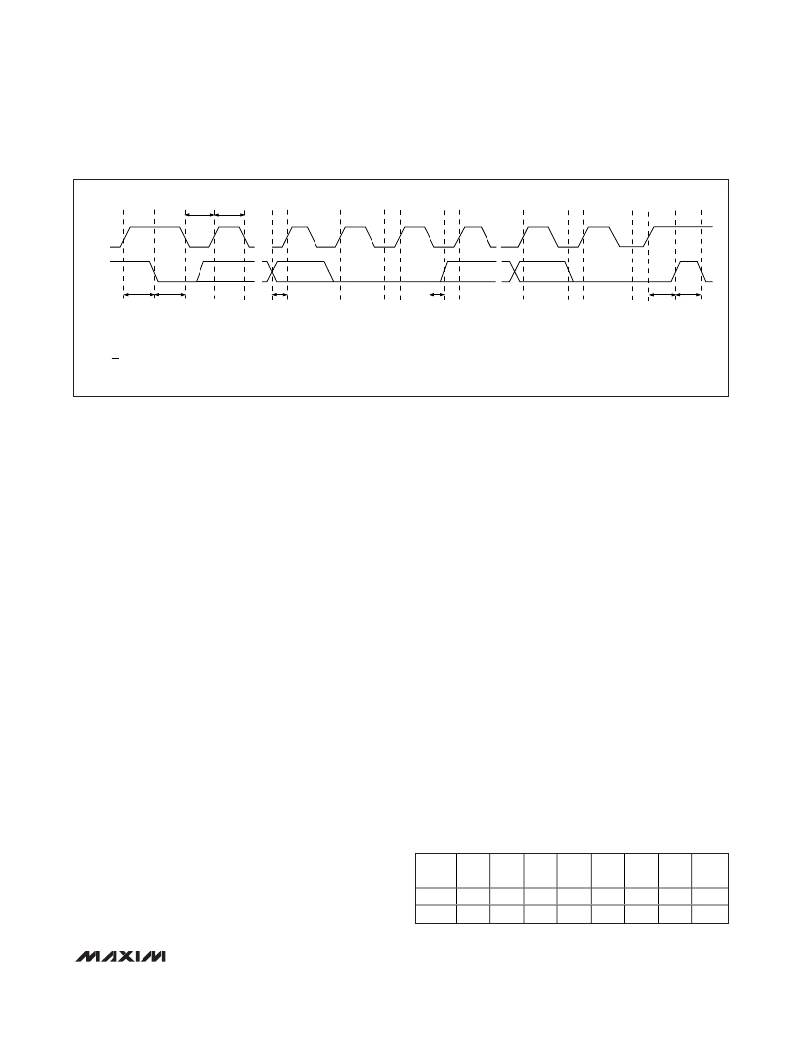

�Table� 3.� Serial� Address�

�is� a� low-to-high� transition� on� SDA� while� SCL� is� high�

�(Figure� 5).� A� START� condition� from� the� master� signals�

�the� beginning� of� a� transmission� to� the� MAX1586/�

�MAX1587.� The� master� terminates� transmission� by� issu-�

�ing� a� not� acknowledge� followed� by� a� STOP� condition�

�SRAD�

�0�

�1�

�A7�

�0�

�0�

�A6�

�0�

�0�

�A5�

�1�

�1�

�A4�

�0�

�0�

�A3�

�1�

�1�

�A2�

�0�

�0�

�A1�

�0�

�1�

�A0�

�RD/� W�

�0�

�0�

�______________________________________________________________________________________�

�23�

�相关PDF资料 |

PDF描述 |

|---|---|

| MAX1587CETL+T | IC POWER MANAGEMENT 40-TQFN |

| H3AWH-2036G | IDC CABLE - HSC20H/AE20G/HPL20H |

| SPD42R-563M | INDUCTOR PWR SHIELDED 56UH SMD |

| MAX8660ETL+T | IC POWER MANAGE XSCALE 40-TQFN |

| MAX8660AETL+T | IC POWER MANAGE XSCALE 40-TQFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX1587AEVKIT | 功能描述:直流/直流开关转换器 MAX1587A Evaluation Kit/Evaluation System RoHS:否 制造商:STMicroelectronics 最大输入电压:4.5 V 开关频率:1.5 MHz 输出电压:4.6 V 输出电流:250 mA 输出端数量:2 最大工作温度:+ 85 C 安装风格:SMD/SMT |

| MAX1587AEVSYS | 功能描述:直流/直流开关转换器 High-Efficiency Low-IQ PMICs with Dynamic Core for PDAs and Smartphones RoHS:否 制造商:STMicroelectronics 最大输入电压:4.5 V 开关频率:1.5 MHz 输出电压:4.6 V 输出电流:250 mA 输出端数量:2 最大工作温度:+ 85 C 安装风格:SMD/SMT |

| MAX1587CETL | 功能描述:直流/直流开关调节器 PMICs w/Dynamic Core for PDAs RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

| MAX1587CETL+ | 功能描述:直流/直流开关调节器 PMICs w/Dynamic Core for PDAs RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

| MAX1587CETL+T | 功能描述:直流/直流开关调节器 PMICs w/Dynamic Core for PDAs RoHS:否 制造商:International Rectifier 最大输入电压:21 V 开关频率:1.5 MHz 输出电压:0.5 V to 0.86 V 输出电流:4 A 输出端数量: 最大工作温度: 安装风格:SMD/SMT 封装 / 箱体:PQFN 4 x 5 |

发布紧急采购,3分钟左右您将得到回复。