- 您现在的位置:买卖IC网 > PDF目录18726 > MAX2308ETI+T (Maxim Integrated)IC VGA DEMODULATOR 28TQFN-EP PDF资料下载

参数资料

| 型号: | MAX2308ETI+T |

| 厂商: | Maxim Integrated |

| 文件页数: | 11/20页 |

| 文件大小: | 0K |

| 描述: | IC VGA DEMODULATOR 28TQFN-EP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 功能: | 解调器 |

| RF 频率: | 70MHz ~ 300MHz |

| P1dB: | -9dBm |

| 噪音数据: | 6.36dB |

| 电流 - 电源: | 41.5mA |

| 电源电压: | 2.7 V |

| 封装/外壳: | 28-WFQFN 裸露焊盘 |

| 供应商设备封装: | 28-TQFN-EP(5x5) |

| 包装: | 带卷 (TR) |

�� �

�

�

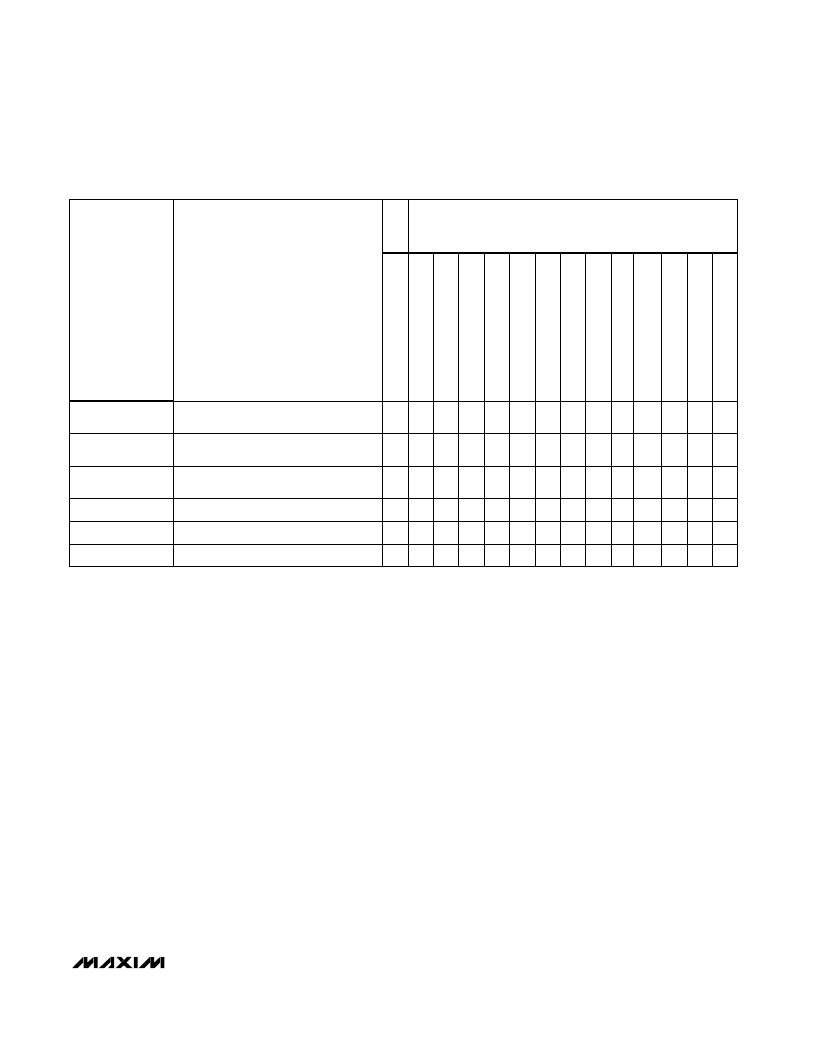

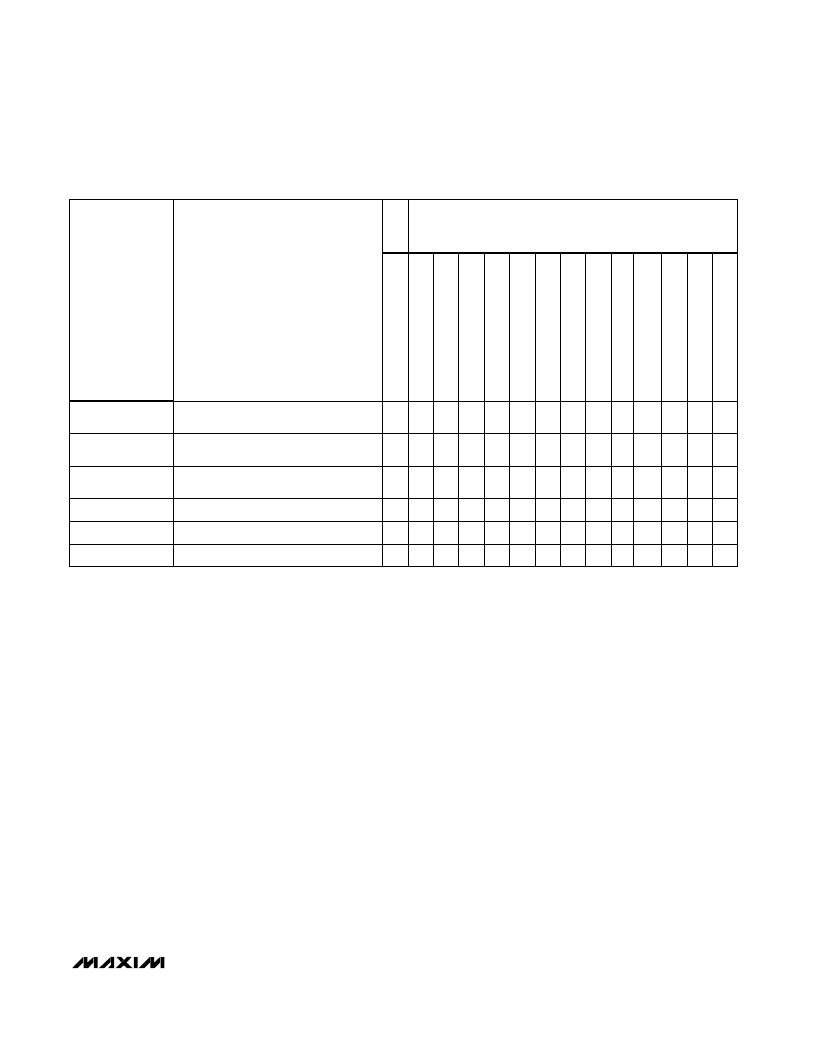

�CDMA� IF� VGAs� and� I/Q� Demodulators�

�with� VCO� and� Synthesizer�

�Table� 2.� MAX2308� Control� Register� States�

�OPERATIONAL�

�MODE�

�ACTION�

�RESULT�

�P�

�I�

�N�

�M�

�S�

�B�

�M�

�CONTROL� S� REGISTER�

�B�

�L�

�S�

�B�

�SHUTDOWN�

�SHUTDOWN�

�Shutdown� pin� completely� shuts� down�

�chip�

�0� in� shutdown� register� bit� leaves� seri-�

�al� port� active�

�L�

�H�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�L�

�STANDBY�

�0� in� standby� pin� turns� off� VGA� and�

�modulator� only�

�H�

�0�

�0�

�X�

�X�

�0�

�1�

�CDMA�

�FM_IQ�

�FM_I�

�CDMA� operation�

�FM� IQ� quadrature� operation�

�FM� I� operation�

�H�

�H�

�H�

�0�

�0�

�0�

�0�

�0�

�0�

�X�

�X�

�X�

�X�

�X�

�X�

�X�

�0�

�1�

�1�

�0�

�0�

�1�

�1�

�1�

�1�

�1�

�1�

�Note:� H� =� high,� L� =� low,� 1� =� logic� high,� 0� =� logic� low,� X� =� don’t� care,� blank� =� independent� parameter�

�When� the� part� initially� powers� up� or� changes� state,� the�

�synthesizer� acquisition� time� can� be� reduced� by� using�

�the� Turbo� feature,� enabled� by� the� TURBOCHARGE�

�(TC)� control� bit.� Turbo� functionality� provides� a� larger�

�charge-pump� current� during� acquisition� mode.� Once�

�the� VCO� frequency� is� acquired,� the� charge-pump� out-�

�put� current� magnitude� automatically� returns� to� the� pre-�

�programmed� state� to� maintain� loop� stability� and�

�minimize� spurs� in� the� VCO� output� signal.�

�The� lock� detect� output� indicates� when� the� PLL� is�

�locked� with� a� logic� high.�

�3-Wire� Interface� and� Registers�

�The� MAX2306� family� incorporates� a� 3-wire� interface� for�

�synthesizer� programming� and� device� configuration�

�(Figure� 5).� The� 3-wire� interface� consists� of� clock,� data,�

�and� enable� signals.� It� controls� the� VCO� dividers� (M1�

�and� M2),� reference� frequency� dividers� (R1� and� R2),�

�and� a� 13-bit� control� register.� The� control� register� is�

�used� to� set� up� the� operational� modes� (Table� 4).� The�

�input� shift� is� 17� data� bits� long� and� requires� a� total� of� 18�

�clock� bits� (Figure� 6).� A� single� clock� pulse� is� required�

�before� enable� drops� low� to� initialize� the� data� bus.�

�Whenever� the� M� or� R� divide� register� value� is� pro-�

�grammed� and� downloaded,� the� control� register� must�

�also� be� subsequently� updated.� This� prevents� turbolock�

�from� going� active� when� not� desired.�

�The� SHDN� control� bit� is� notable� because� it� differs� from�

�the� SHDN� pin.� When� the� SHDN� control� bit� is� low,� the�

�registers� and� serial� interface� are� left� active,� retaining�

�the� values� stored� in� the� latches,� while� the� rest� of� the�

�device� is� shut� off.� In� contrast,� the� SHDN� pin,� when� low,�

�shuts� down� everything,� including� the� registers� and� seri-�

�al� interface.� See� Functional� Diagram� .�

�Registers�

�Figure� 7� shows� the� programming� logic.� The� 17-bit� shift�

�register� is� programmed� by� clocking� in� data� at� the� rising�

�edge� of� CLK.� Before� the� shift� register� is� able� to� accept�

�data,� it� must� be� initialized� by� driving� it� with� at� least� one�

�full� clock� cycle� at� the� CLK� input� with� EN� high� (see�

�Figure� 6).� Pulling� enable� low� will� allow� data� to� be�

�clocked� into� the� shift� register;� pulling� enable� high� loads�

�the� register� addressed� by� A0,� A1,� and� A2,� respectively�

�(Figure� 7).� Table� 5� lists� the� power-on� default� values� of�

�all� registers.� Table� 6� lists� the� charge-pump� current,�

�depending� on� CP0� and� CP1.�

�______________________________________________________________________________________�

�11�

�相关PDF资料 |

PDF描述 |

|---|---|

| 0640000045 | SC TOOL KIT ROUND CABLE |

| 9122A | POWER SPLY 0-60V 0-2.5A PROGRAM |

| UPC8233TK-A | IC SIGE:C LNA 6 MINIMOLD |

| 9121A | PWR SUP SNG OUTPUT PROG 20V 5A |

| TC32M5C32K7680 | OSCILLATOR 32.7680 KHZ 1.8V SMD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX2308EVKIT | 功能描述:射频开发工具 MAX2306/8/9 Eval Kit RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V |

| MAX2309EGI | 功能描述:调节器/解调器 RoHS:否 制造商:Texas Instruments 封装 / 箱体:PVQFN-N24 封装:Reel |

| MAX2309EGI-B50070 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

| MAX2309EGI-T | 功能描述:调节器/解调器 RoHS:否 制造商:Texas Instruments 封装 / 箱体:PVQFN-N24 封装:Reel |

| MAX2309ETI+ | 功能描述:调节器/解调器 CDMA If VGAs & I/Q Demodulator w/VCO RoHS:否 制造商:Texas Instruments 封装 / 箱体:PVQFN-N24 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。