- 您现在的位置:买卖IC网 > PDF目录8773 > MAX3625BEUG+ (Maxim Integrated Products)IC PLL CLOCK GEN LO JITT 24TSSOP PDF资料下载

参数资料

| 型号: | MAX3625BEUG+ |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 4/10页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLOCK GEN LO JITT 24TSSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 62 |

| 类型: | 时钟发生器,扇出配送,多路复用器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,晶体 |

| 输出: | LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:3 |

| 差分 - 输入:输出: | 无/是 |

| 频率 - 最大: | 318.75MHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 24-TSSOP(0.173",4.40mm)裸露焊盘 |

| 供应商设备封装: | 24-TSSOP 裸露焊盘 |

| 包装: | 管件 |

MAX3625B

Low-Jitter, Precision Clock

Generator with Three Outputs

_______________________________________________________________________________________

3

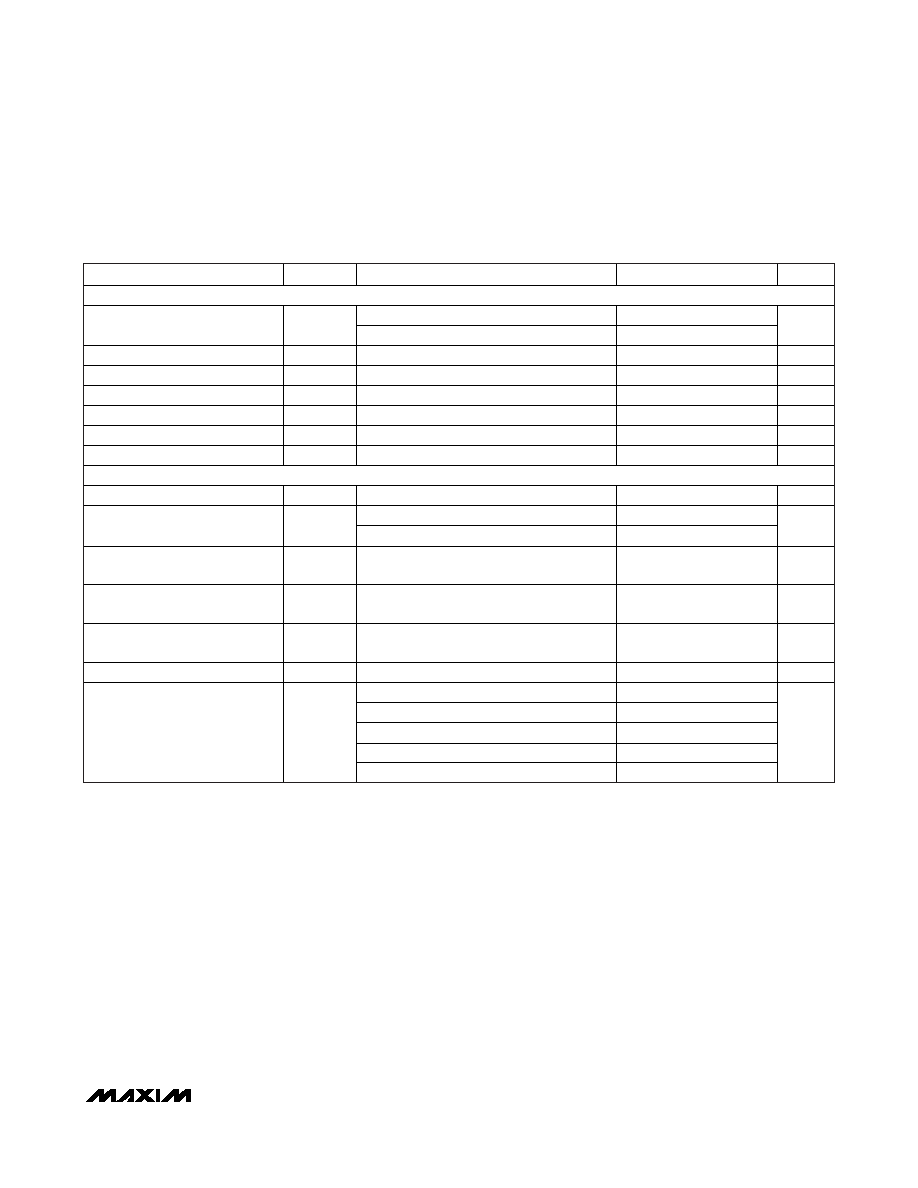

ELECTRICAL CHARACTERISTICS (continued)

(VCC = +3.0V to +3.6V, TA = -40°C to +85°C, unless otherwise noted. Typical values are at VCC = +3.3V, TA = +25°C, unless other-

wise noted.) (Notes 1, 2)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

REF_IN SPECIFICATIONS (Input DC- or AC-Coupled)

PLL enabled

24.8

27.0

Reference Clock Frequency

PLL bypassed

320

MHz

Input-Voltage High

VIH

2.0

V

Input-Voltage Low

VIL

0.8

V

Input High Current

IIH

VIN = VCC

240

μA

Input Low Current

IIL

VIN = 0V

-240

μA

Reference Clock Duty Cycle

PLL enabled

30

70

%

Input Capacitance

2.5

pF

CLOCK OUTPUT AC SPECIFICATIONS

VCO Frequency Range

620

648

MHz

12kHz to 20MHz

0.36

1.0

Random Jitter (Note 5)

RJRMS

1.875MHz to 20MHz

0.14

psRMS

Spurs Induced by Power-Supply

Noise

(Notes 6, 7, 8)

-60

dBc

Deterministic Jitter Induced by

Power-Supply Noise

(Note 9)

5.6

psP-P

Nonharmonic and Subharmonic

Spurs

-70

dBc

Output Skew

Between any output pair

5

ps

f = 1kHz

-124

f = 10kHz

-127

f = 100kHz

-131

f = 1MHz

-145

Clock Output SSB Phase Noise

at 125MHz (Note 10)

f > 10MHz

-153

dBc/Hz

Note 1:

A series resistor of up to 10.5

Ω is allowed between VCC and VCCA for filtering supply noise when system power-supply

tolerance is VCC = 3.3V ±5%. See Figure 1.

Note 2:

LVPECL outputs guaranteed up to 320MHz.

Note 3:

All outputs enabled and unloaded.

Note 4:

Measured with a crystal (see Table 4) or an AC-coupled, 50% duty-cycle signal on REF_IN.

Note 5:

Measured with crystal source, see Table 4.

Note 6:

Measured using setup shown in Figure 1.

Note 7:

Measured with 40mVP-P, 100kHz sinusoidal signal on the supply.

Note 8:

Measured at 156.25MHz output.

Note 9:

Calculated based on measured spurs induced by power-supply noise (refer to Application Note 4461:

HFAN-04.5.5:

Characterizing Power-Supply Noise Rejection in PLL Clock Synthesizers).

Note 10: Measured with 25MHz crystal or 25MHz reference clock at REF_IN with a slew rate of 0.5V/ns or greater.

相关PDF资料 |

PDF描述 |

|---|---|

| D38999/26JJ19SNLC | CONN HSG PLUG 19POS STRGHT SCKT |

| VI-J23-MZ-F2 | CONVERTER MOD DC/DC 24V 25W |

| VI-24H-MW-F3 | CONVERTER MOD DC/DC 52V 100W |

| D38999/26MJ19BN | CONN HSG PLUG 19POS STRGHT SCKT |

| VI-24H-MW-F2 | CONVERTER MOD DC/DC 52V 100W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX3625BEUG+ | 功能描述:时钟发生器及支持产品 Low Jitter Precision w/Four Outputs RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MAX3625BEUG+T | 功能描述:时钟发生器及支持产品 Low Jitter Precision w/Four Outputs RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MAX3625BEVKIT+ | 功能描述:时钟发生器及支持产品 Not Available From Mouser RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MAX3625CUG+ | 功能描述:时钟发生器及支持产品 Not Available From Mouser RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MAX3625CUG+T | 功能描述:时钟发生器及支持产品 Not Available From Mouser RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。